IEEE TRANSACTIONS ON INDUSTRIAL INFORMATICS

# Sensor-Less Five-Level Packed U-Cell (PUC5) Inverter Operating in Stand-Alone and Grid-Connected Modes

Hani Vahedi, Student, IEEE, Philippe-Alexandre Labbé, Kamal Al-Haddad, Fellow, IEEE

Abstract-In this paper a new mode of operation has been introduced for Packed U-Cell (PUC) inverter. A sensor-less voltage control based on redundant switching states is designed for the PUC5 inverter which is integrated into switching process. The sensor-less voltage control is in charge of fixing the DC capacitor voltage at half of the DC source value results in generating symmetric five-level voltage waveform at the output with low harmonic distortion. The sensor-less voltage regulator reduces the complexity of the control system which makes the proposed converter appealing for industrial applications. An external current controller has been applied for grid-connected application of the introduced sensor-less PUC5 to inject active and reactive power from inverter to the grid with arbitrary power factor while the PUC auxiliary DC bus is regulated only by sensor-less controller combined with new switching pattern. Experimental results obtained in stand-alone and grid-connected operating modes of proposed PUC5 inverter prove the fast response and good dynamic performance of the designed sensorless voltage control in balancing the DC capacitor voltage at desired level.

*Index Terms*—Multilevel Inverter, Packed U-Cell, Sensor-Less Voltage Regulator, PUC5, 5-Level Inverter, Power Quality.

### I. INTRODUCTION

High harmonic content of output voltage waveform in conventional two-level inverters is a matter of controversy. Nowadays, using more switches and DC sources in power electronics converters is a competitive field of research leads to generate more voltage levels at the output and consequently lower harmonic content, smaller size of the output filters, and lower manufacturing cost as well [1, 2]. Multilevel inverters are designed based on configuration of more switches and DC supplies to achieve the goal of generating various voltage levels at the output. Such inverters generate low harmonic waveforms; therefore they are most suitable for energy conversion applications to deliver efficient power to the loads from renewable energy sources like photovoltaic systems [3-6].

Copyright © 2015 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending a request to pubs-permissions@ieee.org.

This work has been supported by the Canadian Research Chair in Electric Energy Conversion and Power Electronics (CRC-EECPE).

H. Vahedi, P.A. Labbé and K. Al-Haddad are with the Ecole de Technologie Superieure, University of Quebec, Montreal, Quebec, Canada H3C 1K3 (email: hani.vahedi@etsmtl.ca, labbe.philippealexandre.1990@ieee.org, kamal.al-haddad@etsmtl.ca) The main problem of multilevel converters is having more independent DC supplies than the conventional two-level ones that make the use of bulky transformers and diode rectifiers inevitable. Besides, complicated voltage control strategies must be applied in case of using DC capacitors instead of DC sources [7-9].

Researchers have been introducing lots of multilevel inverter topologies also for low and medium power applications like connecting photovoltaic panels to the local grid as household consumption or street lightings to convert the DC voltage of the renewable energy resource to the proper AC waveform useable at load and grid sides. In such applications a single-phase transformer-less inverter with minimum number of DC sources is preferable [10-19]. Packed U-Cell (PUC) inverter has been first introduced by Al-Haddad et al to generate 7-level voltage while using only 6 active switches, one isolated DC sources and one capacitor as second source which its voltage should be controlled to fix at 1/3 of first DC source [20]. Although the mentioned topology has less number of components among other 7-level inverters, it has some major drawbacks including high switching frequency, asymmetric output voltage cycles and levels, requiring fast response and complicated controller with lot of feedback sensors, using large capacitor to regulate the voltage in variable situations and etc [18, 21, 22].

In this paper, the PUC topology is investigated to have simple controller and better performance, which led to proposing a new self-voltage-balancing sensor-less 5-level PUC inverter called sensor-less PUC5. The PUC5 inverter capacitor voltage would be fixed at half of the DC source amplitude using a self-voltage-balancing process which is integrated into the multicarrier pulse width modulation (PWM). Therefore there would be no necessity of using voltage or current sensors due to not using complicated controllers. Since the capacitor voltage is kept constant at desired level, the output voltage waveform would have symmetrical five levels with less harmonic distortion. The PUC5 topology and proposed technique is the subject of a US provisional patent application No.: 62/073387 which is explained and fully investigated in section II. In section III, grid-connected controller is described. Section IV includes some comparative study between multilevel inverters based on number of components. The experimental results including stand-alone and grid-connected modes are shown and discussed in section V to demonstrate the fast and good dynamic performance of proposed sensor-less self-voltage-

Manuscript received November 10, 2014; revised July 02, 2015; accepted September 06, 2015.

<sup>© 2016</sup> IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

# IEEE TRANSACTIONS ON INDUSTRIAL INFORMATICS

balancing technique applied on PUC5 inverter in regulating the capacitor voltage at desired level and producing five-level output voltage in face of varying conditions.

# II. PROPOSED PUC5 INVERTER TOPOLOGY AND SELF-VOLTAGE-BALANCING SWITCHING TECHNIQUE

Although the 7-level output waveform of the PUC is interesting due to generating maximum voltage levels while using minimum number of components, requiring complex controller and many sensors to provide state feedbacks for controller calculation as well as asymmetric voltage levels produced make it difficult to get wide spread acceptance by the industries and market.

### A. PUC5 Inverter Configuration and Sensor-Less Voltage Balancing Investigation

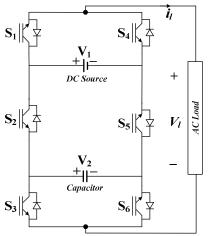

The single-phase PUC inverter topology has been shown in Fig. 1. The complete associate switching states are listed in table I [20].

Fig. 1: PUC inverter topology

| SSIBLE SWIT    | ICHING ST<br>S <sub>3</sub><br>0 | ATES OF PUC IN<br>Output<br>Voltage<br>V.             | VVERTER<br>V <sub>1</sub><br>+2E                     |

|----------------|----------------------------------|-------------------------------------------------------|------------------------------------------------------|

| S <sub>2</sub> | S <sub>3</sub><br>0              |                                                       | • 1                                                  |

| 0              | 0                                | V.                                                    | 100                                                  |

|                |                                  | ¥ 1                                                   | +2E                                                  |

| 0              | 1                                | $V_1-V_2$                                             | +E                                                   |

| 1              | 0                                | $V_2$                                                 | +E                                                   |

| 1              | 1                                | 0                                                     | 0                                                    |

| 0              | 0                                | 0                                                     | 0                                                    |

| 0              | 1                                | -V <sub>2</sub>                                       | -E                                                   |

| 1              | 0                                | $V_2-V_1$                                             | -Е                                                   |

| 1              | 1                                | $-V_1$                                                | -2E                                                  |

| ,              | 1<br>1<br>0<br>0<br>1<br>1       | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

It is clear that 8 existing switching states can provide different paths for current to flow through the system including DC sources and load. Taking into account that the output voltage levels numbers depend on DC sources amplitudes, using unequal DC sources result in having different level numbers in output voltage waveform. First, to have maximum number of levels at the output, V<sub>2</sub> amplitude must be 1/3 of V<sub>1</sub>. Assuming V<sub>1</sub>=3V<sub>2</sub>=3E, seven levels would be generated as 0,  $\pm$ E,  $\pm$ 2E,  $\pm$ 3E. 7-level PUC disadvantages were mentioned above which is mostly due to complex voltage balancing procedure, but considering table I more precisely, it is observed that the PUC inverter has the ability to operate as 5-level inverter by assuming  $V_1=2V_2=2E$ , therefore the output 5-level voltage waveform includes the levels 0, ±E, ±2E. In this case, the capacitor voltage ( $V_2$ ) is kept constant at half of the DC source ( $V_1$ ) amplitude. Noticing table I, six switching states are available to produce three levels including -E, 0 and +E that means there are some redundant switching states which may help to find different paths for flowing current through the load. The redundant switching states can deal with charging and discharging the capacitor in order to balance the voltage at the half of the DC source voltage.

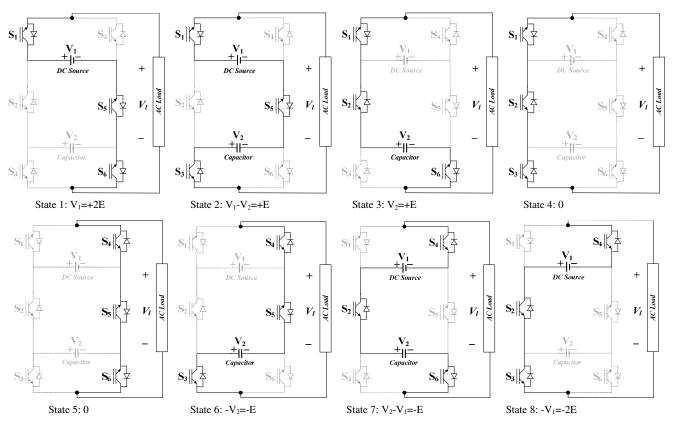

To use the redundant switching states in proper design of the required PWM technique for PUC5 inverter, all switching states have been studied noticing the effects on capacitor voltage. Fig. 2 shows the paths made by switching states listed in table I.

Based on Fig. 2, it is clear that in states where the DC source and capacitor are connected in series with the load, the capacitor is charged (states 2 & 7). On the other hand, on some paths that the capacitor feeds the load alone, it is discharging (states 3 & 6). Eventually, for rest of the states, the capacitor voltage is remained unchanged because it is neither connected to DC source nor to the load. Table II indicates the charging and discharging states of the capacitor.

| - | TABLE II |                          |  |  |  |  |  |

|---|----------|--------------------------|--|--|--|--|--|

|   | CAPAC    | CAPACITOR VOLTAGE STATES |  |  |  |  |  |

|   | State    | Capacitor Voltage        |  |  |  |  |  |

|   | 1        | No Effect                |  |  |  |  |  |

|   | 2        | Charging                 |  |  |  |  |  |

|   | 3        | Discharging              |  |  |  |  |  |

|   | 4        | No Effect                |  |  |  |  |  |

|   | 5        | No Effect                |  |  |  |  |  |

|   | 6        | Discharging              |  |  |  |  |  |

|   | 7        | Charging                 |  |  |  |  |  |

|   | 8        | No Effect                |  |  |  |  |  |

|   |          |                          |  |  |  |  |  |

One of the main issues with 7-level PUC inverter in balancing the capacitor voltage is high switching frequency, complexity of the controller and using too many sensors as states variables feedbacks [21, 23]. Since the investigated PUC5 inverter has redundant switching states, the capacitor voltage balancing feature can be integrated into the modulation technique. Therefore the control strategy contains only the PWM switching technique without the necessity of using additional controller (linear or nonlinear or ...) which necessitates complex function and more computation effort of the real time controller therefore makes it not simple to implement. It is expected that the voltage controller integrated into switching technique would have good dynamic performance and fast response due to simplicity and not using any feedback sensors.

The key point in table II is the fact that capacitor can be charged or discharged in each positive or negative half cycle. Therefore, in order to keep the capacitor voltage fixed, in designing of proposed switching technique, it has been decided to charge the capacitor in the positive half-cycle and then to discharge it in negative half cycle. Due to the output voltage waveform frequency which is 60 Hz and the selected switching frequency, the capacitor can be only charged to half of the DC source amplitude.

<sup>1551-3203 (</sup>c) 2015 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

IEEE TRANSACTIONS ON INDUSTRIAL INFORMATICS

Fig. 2: switching states and conducting paths of PUC5 inverter

Regarding the charging states (2 and 7), it is clear that the capacitor is charged when it is connected in series with DC source and load, as well as the load voltage should be  $\pm E$ . Thus the following equations can be written:

$$V_1 = V_2 + V_l \implies \begin{cases} 2E = V_2 + E \\ -2E = V_2 - E \end{cases} \Rightarrow |V_2| = E$$

(1)

While the source voltage is fixed at 2E, the capacitor must be charged up to E to produce the proper output load voltage. Such condition as well as the charging (discharging) time forces the capacitor to charge up to half of source voltage value.

In order to have equivalent times of charging and discharging in one period, switching state 2 is chosen to connect the DC source to the capacitor and charge it up, while on the other hand, the capacitor will be discharged in negative half cycle in order to prevent the overcharged through the switching state 6 which connects the capacitor directly to the load. The mentioned procedure is independent of the switching frequency and output voltage frequency. The capacitor charging and discharging time only depends on load value. It has direct effect on capacitor size which should be considered in calculating the system parameters for specific application design. Larger loads need smaller capacitor in DC link and vice versa.

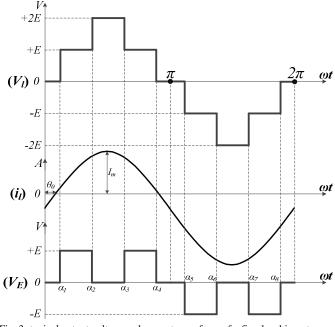

This self-voltage-balancing procedure can be mathematically proved based on capacitor energy relations. Fig. 3 shows one cycle of the typical output voltage and current waveforms of PUC5 inverter.  $V_E$  is a part of output

voltage generated by the capacitor (+E or -E) whether connected to the load alone as discharging path or in series with DC source as charging process.

Fig. 3: typical output voltage and current waveform of a five-level inverter

The output voltage and current can be assumed as a following sine functions:

$$v_l(t) = V_m Sin(\omega t) \tag{2}$$

$$i_l(t) = I_m \operatorname{Sin}(\omega t \cdot \theta_0) \tag{3}$$

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TII.2015.2491260, IEEE Transactions on Industrial Informatics

# IEEE TRANSACTIONS ON INDUSTRIAL INFORMATICS

Where,  $V_m$  and  $I_m$  are the maximum value of output voltage and current waveforms, respectively. As well,  $\theta_0$  is the phase difference between output voltage and current. Based on energy absorbing or delivering to the load by dc capacitor, the following equations can be written:

$$I = \frac{dq}{dt}$$

$$\rightarrow dU = V \, dq = V \, I \, dt$$

(4)

$$\rightarrow U = \int V \, I \, dt$$

Where, I, q, and U are current, electric charge, voltage and energy of the capacitor, respectively. Considering Fig. 3 and substituting equation (3) into (4), the capacitor energy delivered or absorbed in PUC5 inverter can be derived in periods of positive and negative half-cycle of the output voltage. It should be also mentioned that the capacitor voltage is a fixed value at E.

$$\begin{split} U^{+} &= \int_{0}^{\pi} V_{E} I_{m} Sin(\omega t - \theta_{0}) d(\omega t) \\ &= I_{m} \int_{0}^{\pi} V_{E} Sin(\omega t - \theta_{0}) d(\omega t) \\ &= \int_{0}^{\alpha_{1}} 0 \times Sin(\omega t - \theta_{0}) d(\omega t) \\ &+ \int_{\alpha_{1}}^{\alpha_{2}} E \times Sin(\omega t - \theta_{0}) d(\omega t) \\ &+ \int_{\alpha_{1}}^{\alpha_{3}} 0 \times Sin(\omega t - \theta_{0}) d(\omega t) \\ &+ \int_{\alpha_{3}}^{\pi} 0 \times Sin(\omega t - \theta_{0}) d(\omega t) \\ &+ \int_{\alpha_{4}}^{\pi} 0 \times Sin(\omega t - \theta_{0}) d(\omega t) \\ &= -EI_{m} Cos(\omega t - \theta_{0}) |_{\alpha_{1}}^{\alpha_{2}} - EI_{m} Cos(\omega t - \theta_{0}) |_{\alpha_{3}}^{\alpha_{4}} \\ &= EI_{m} \left[ \begin{array}{c} Cos(\alpha_{1} - \theta_{0}) - Cos(\alpha_{2} - \theta_{0}) \\ + Cos(\alpha_{3} - \theta_{0}) - Cos(\alpha_{4} - \theta_{0}) \end{array} \right] \end{split}$$

The same effort is done for calculating capacitor energy in negative half-cycle and the following equation would be obtained for  $U^{-}$ :

$$U^{-} = \int_{\pi}^{2\pi} V_{E} I_{m} Sin(\omega t - \theta_{0}) d(\omega t)$$

=  $I_{m} \int_{\pi}^{2\pi} V_{E} Sin(\omega t - \theta_{0}) d(\omega t)$

=  $E I_{m} Cos(\omega t - \theta_{0}) |_{\alpha_{5}}^{\alpha_{6}} + E I_{m} Cos(\omega t - \theta_{0}) |_{\alpha_{7}}^{\alpha_{8}}$

=  $E I_{m} \begin{bmatrix} Cos(\alpha_{6} - \theta_{0}) - Cos(\alpha_{5} - \theta_{0}) \\ + Cos(\alpha_{8} - \theta_{0}) - Cos(\alpha_{8} - \theta_{0}) \end{bmatrix}$  (6)

Noticing the fact that two half cycles of the output voltage are symmetric, thus it can be assumed that:

$$\begin{cases}

\alpha_5 = \pi + \alpha_1 \\

\alpha_6 = \pi + \alpha_2 \\

\alpha_7 = \pi + \alpha_3 \\

\alpha_8 = \pi + \alpha_4

\end{cases}$$

(7)

Then the energy amount in half cycles would be equal in value but opposite in sign:

$$U^{-} = -U^{+} \tag{8}$$

This means that the capacitor energy in full cycle would be balanced and maintained constant which leads to keep the capacitor voltage at the desired level in all conditions since the reference waveform is periodical.

Higher switching frequency implies more switching pulses make the capacitor charging/discharging time smaller; consequently better voltage balancing performance. Since the sensor-less voltage balancing concept is based on the symmetry of the charging and discharging times it is therefore independent of the grid voltage distortion or unbalanced voltage conditions where the full cycle is reformed (eg the 3<sup>rd</sup> or 5<sup>th</sup> harmonic are present). In such conditions, both positive and negative half cycles are still identical and symmetrical results in self-voltage-balancing of the capacitor eventually.

# *B.* Sensor-Less Voltage Controller Integrated Into Switching Technique

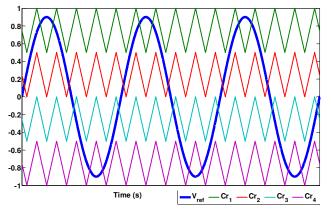

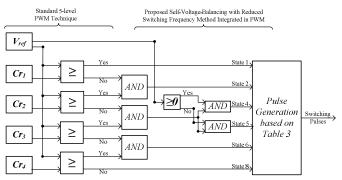

Five-level PWM scheme including four carriers' waves and the sinusoidal reference waveform is depicted in Fig. 4. The four carriers' waveforms (Cr<sub>1</sub>, Cr<sub>2</sub>, Cr<sub>3</sub>, and Cr<sub>4</sub>) are shifted vertically to modulate the reference waveform (V<sub>ref</sub>) completely [15, 24]. The firing pulses associated with switching states 1, 2, 4, 5, 6 and 8 (listed in table I) are generated based on comparing V<sub>ref</sub> with those carrier waves. Moreover, redundant switching states of 4 and 5 are used to reduce the switching frequency. If V<sub>ref</sub> is positive, then state 4 will be used to produce the zero level at the output. On the other hand, if V<sub>ref</sub> is negative, the output zero level voltage will be generated by state 5. The described algorithm is shown in Fig. 5 which can produce the five-level voltage waveform at the output with minimum switching frequency while fixing the

(5)

#### IEEE TRANSACTIONS ON INDUSTRIAL INFORMATICS

capacitor voltage at the desired level without any feedback sensor.

Fig. 4: five-level PWM scheme using four vertically shifted carrier waveforms

Fig. 5: proposed open-loop switching algorithm for self-voltage-balancing of PUC5 Inverter

As mentioned before, applying the proposed algorithm on PUC5 inverter generates 5-level voltage waveform at the output without using any voltage sensors and complex calculations in controller. The capacitor voltage would be constant even at start-up and also in load change conditions. The light algorithm makes the system much faster than previously implemented controller on PUC inverter as published in the literature. The proposed technique does not depend on system model (e.g. average modelling), feedback sensors, modulation index, switching frequency and grid frequency. It can operate the system starting from zero voltage up to arbitrary amplitude and also in DC source voltage variation situations.

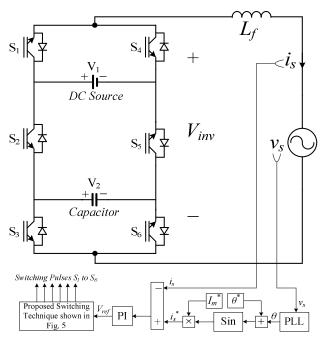

# III. GRID-CONNECTED MODE CONFIGURATION AND CONTROLLER

The grid-connected PUC5 inverter with associated controller is shown in Fig. 6 in which  $i_s$  is the injected current from inverter to the grid. The typical controller has been designed to control the amplitude and phase-shift of  $i_s$  results in delivering active power and exchanging reactive power desirably with the grid by PUC5 inverter. Even in this controller the DC capacitor voltage is not involved since proposed technique in previous section is in charge of balancing this voltage [25-27].

Fig. 6: Grid-connected PUC5 inverter with designed controller

In illustrated controller, AC source voltage  $(v_s)$  is measured and sent to the PLL to extract its phase angle. The grid voltage angle is then added to the desired phase shift denoted as  $\theta^*$ . to exchange reactive power with the grid while injecting active power, power factor (PF) should be between 0 and 1 which can be determined by  $\theta^*$ . If the unity power factor mode of operation is targeted, therefor  $\theta^* = 0$  to ensure an injected grid current synchronized with  $v_s$ . For reactive power exchange the power factor should be less than 1. For instance, to have a PF = 0.5 then  $\theta^* = 60^\circ$  should be added to the measured voltage angle. The reference angle is sent to the Sin block to produce a unit sine wave containing desired phase shift. This unit sine wave is multiplied by desired value as maximum reference current  $(I_m^*)$  which can control the amount of power injected to the grid. The resulted function is assumed as reference current  $(i_s^*)$  that should be generated by the inverter. The actual current  $(i_s)$  is compared with reference current and the error signal is sent to a proportional-integral linear controller to minimize the steady state error. The PI controller output signal will be modulated by the proposed switching technique shown in Fig. 5 which is also responsible in balancing the PUC5 capacitor voltage at half of the DC source amplitude.

PUC5 inverter is expected to generate lower harmonic current waveform injecting to the grid compared to conventional single-phase full-bridge grid-connected inverters due to generating more voltage levels at the output.

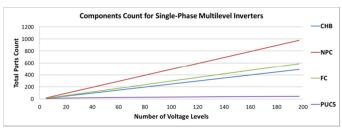

#### IV. COMPARATIVE STUDY OF MULTILEVEL INVERTER BASED ON NUMBER OF COMPONENTS

Table III shows the components count in popular multilevel inverters as well as the proposed PUC5 inverter in case of producing single-phase 5-level output voltage waveform. It is prominent that the proposed converter with the sensor-less voltage balancing technique has the less components as well as its control complexity is very low.

#### IEEE TRANSACTIONS ON INDUSTRIAL INFORMATICS

Extending to the n-level, table IV will be achieved. Component counts are calculated in term of voltage level (n). It should be mentioned that in more than 3-level inverters, no reliable control techniques have been reported for NPC since all of them have some limitations on load power factor and modulation index [28]. Although it has been compared in Table III, it is not listed in the Table IV for higher voltage levels. Moreover, the proposed PUC5 inverter is able to produce voltage levels using binary DC links so it would have the levels like 5, 10, 17, 26, ... [29-31].

The following chart in Fig. 7 demonstrates the low number of components used in PUC5 inverter rising by the voltage levels. It is observed that the number of components employed in PUC5 is slowly raised as a function of the produced voltage levels.

| TABLE III                                              |              |           |                  |                  |                         |                       |

|--------------------------------------------------------|--------------|-----------|------------------|------------------|-------------------------|-----------------------|

| COMPONENTS COUNT FOR SINGLE-PHASE FIVE-LEVEL INVERTERS |              |           |                  |                  |                         |                       |

| Inverter Type                                          | DC<br>Source | Capacitor | Clamped<br>Diode | Active<br>Switch | Total<br>Parts<br>Count | Control<br>Complexity |

| CHB                                                    | 2            | 0         | 0                | 8                | 10                      | Low                   |

| NPC with voltage control                               | 1            | 4         | 6                | 8                | 19                      | Very High             |

| NPC without voltage control                            | 4            | 0         | 6                | 8                | 18                      | Low                   |

| FC                                                     | 1            | 3         | 0                | 8                | 12                      | High                  |

| Proposed PUC5                                          | 1            | 1         | 0                | 6                | 8                       | Very Low              |

|                                                        |              |           |                  |                  |                         |                       |

| TABLE IV                                               |                 |                    |                  |                    |                      |  |

|--------------------------------------------------------|-----------------|--------------------|------------------|--------------------|----------------------|--|

| COMPONENTS COUNT FOR SINGLE-PHASE MULTILEVEL INVERTERS |                 |                    |                  |                    |                      |  |

| Inverter Type                                          | DC<br>Source    | Capacitor          | Clamped<br>Diode | l Active<br>Switch | Total Parts<br>Count |  |

| СНВ                                                    | $\frac{n-1}{2}$ | 0                  | 0                | 2(n-1)             | $\frac{5(n-1)}{2}$   |  |

| NPC without voltage control                            | <i>n</i> -2     | 0                  | 2(n-2)           | 2(n-1)             | 5n-7                 |  |

| FC                                                     | 1               | <i>n</i> -2        | 0                | 2(n-1)             | 3(n-1)               |  |

| Proposed PUC5                                          | 1               | $\sqrt{n - 1} - 1$ | 0                | $2\sqrt{n-1} + 2$  | $2 \sqrt{n-1} + 2$   |  |

Fig. 7: components count chart in multilevel inverters

As a comparison only between 7-level PUC inverter and the proposed PUC5, it should be noted that the 7-level PUC needs a very complicated controller to produce desired voltage levels at the output which requires adjusting a lot of controller gains in practical works. Moreover, the controller design needs a lot of effort in modelling the system accurately and using many state variable feedbacks that increase the number of state variables and consequently voltage and current sensors. Moreover, It is highly dependent on the system parameters including load, connection line resistance and inductance, switching frequency, sampling time, DC source voltage amplitude, DC capacitor value, modulation index and output voltage frequency. It can show improper results containing a lot of spikes on the generated voltage waveform, which makes use of additional protection device inevitable. All in all, the 7level PUC inverter needs more investigation and improvement to be useful in all conditions. On the other hand, the proposed 5-level functionality of the PUC inverter illustrates proper results in all stand-alone and grid-connected conditions without using additional feedback sensors to balance internal DC bus voltage. However, it should be mentioned that the sensor-less voltage balancing is only about the internal capacitor voltage control of the converter and it does not imply on any other external sensors such as shown in Fig. 6 to control the line current. Less complex controller combined with lower switching frequency are some advantages of the proposed PUC5 inverter with requiring less components count as well.

#### V. EXPERIMENTAL RESULTS

A prototype of PUC inverter has been built to validate the proposed PUC5 with self-voltage-balancing in both standalone and grid-connected modes. Six 1.2KV 40A SiC MOSFETs type SCT2080KE have been used as active switches. The proposed self-voltage balancing procedure integrated into switching technique and the designed gridconnected controller has been applied by dSpace 1103 as realtime controller and switching pulses are sent to the PUC5 switches. The tested system parameters are listed in table V.

| TABLE V<br>Experimental system parameters                              |             |  |  |  |

|------------------------------------------------------------------------|-------------|--|--|--|

| Grid Voltage (v <sub>s</sub> )                                         | 110 V rms   |  |  |  |

| Grid Frequency                                                         | 60 Hz       |  |  |  |

| Grid Link Inductor (L <sub>f</sub> )                                   | 4 mH        |  |  |  |

| DC Source Voltage (V <sub>1</sub> )                                    | 200 V       |  |  |  |

| Switching Frequency                                                    | 2 kHz       |  |  |  |

| Stand-Alone mode RL Load                                               | 40 Ω, 20 mH |  |  |  |

| Stand-Alone mode Rectifier Load (DC Side $R_{dc} \mbox{ and } L_{dc})$ | 40 Ω, 50 mH |  |  |  |

| DC Capacitor                                                           | 2500 µF     |  |  |  |

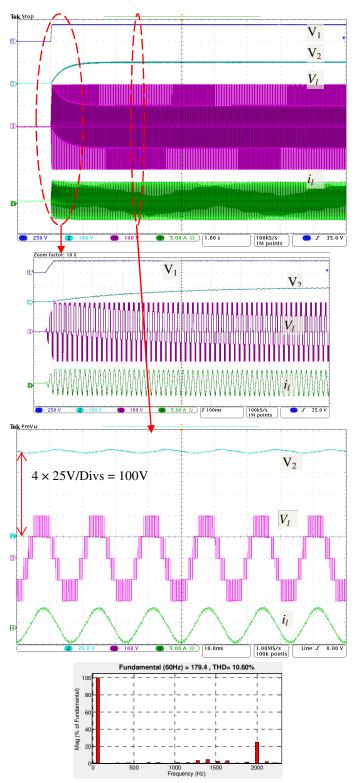

#### A. Test 1: Stand-Alone Mode

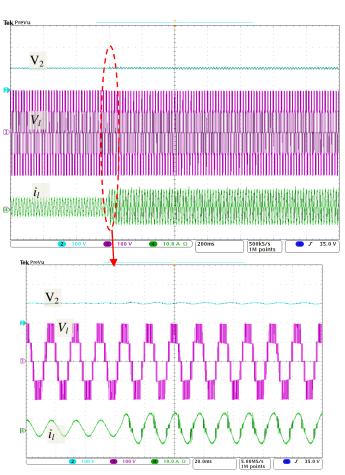

The PUC5 inverter has been tested under various load conditions such as stand-alone mode as UPS application including change in load and in DC source. In this mode, the PUC5 inverter supplies an RL type of load.

At first, the start-up mode of the PUC5 inverter is shown in Fig. 8. The capacitor is charged up to half of DC source by proposed sensor-less voltage balancing approach and fivelevel output voltage is generated symmetrically. Results show that no pre-charged capacitor is needed in this topology with the implemented voltage control. Moreover, the zoomed figure shows that the capacitor voltage ripple is less than 5%. The FFT analysis of the 5-level inverter voltage waveform has been performed and its harmonic spectrum is shown in Fig. 8. It should be mentioned that the output voltage THD is about 10% without adding additional bulky harmonic filters. 2 kHz frequency of the PWM carriers is clear in this figure as the highest amplitude of the harmonic orders except the fundamental one.

IEEE TRANSACTIONS ON INDUSTRIAL INFORMATICS

Fig. 8: start-up capacitor charging, 5-level voltage generating and FFT analysis

In another test, a nonlinear load consisting of a single-phase rectifier connected to  $R_{dc}$  and  $L_{dc}$  on its DC side is connected in parallel to the existing RL load and they are feed by PUC5 inverter. Results are illustrated in Fig. 9 that demonstrate the good dynamic performance of proposed technique in variable load conditions.

Fig 9: adding single-phase rectifier (as nonlinear load) paralleled with the RL load to the output of PUC5

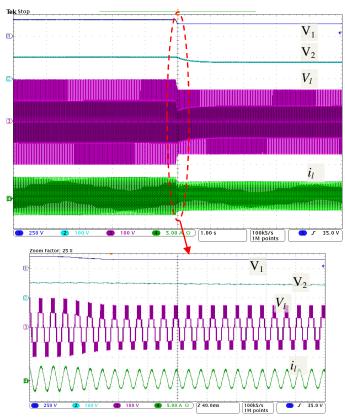

Fig. 10 contains results when the DC source voltage is changing and capacitor voltage is tracking the reference value  $(V_1/2)$  properly by applying proposed sensor-less voltage regulator technique integrated into switching pattern.

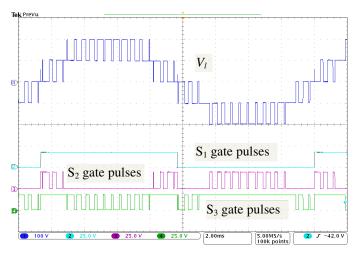

Finally, in stand-alone mode, switches gate pulses as well as one cycle of output voltage are depicted in Fig. 11. It is clear that two upper switches are operating at grid frequency while their voltage rating as equal to DC source voltage (V<sub>1</sub>). Although, four lower switches are fired with higher frequency than upper switches, the switching frequency is not that large compared to 2-level conventional inverters [32, 33]. Moreover, their voltage ratings are half of two upper switches that they have to withstand capacitor voltage which is  $V_1/2$ .

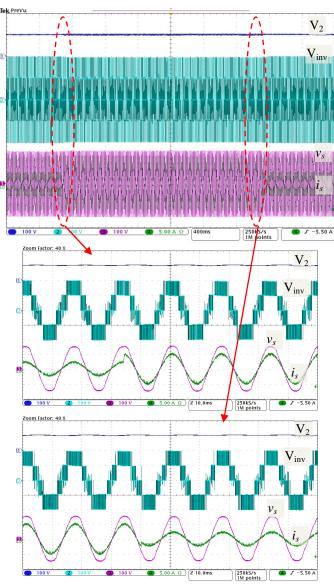

#### B. Test 2: Grid-Connected Mode

In this case, the PUC5 inverter is connected to a singlephase AC source as grid and the designed controller in section III is forcing the inverter to inject power to the grid with different power factor. At first, to show the fast response and proper dynamic performance of designed grid-connected controller as well as proposed sensor-less voltage balancing technique,  $\theta^* = 0$  is selected and the current reference is changed during the test as illustrated in Fig. 12.

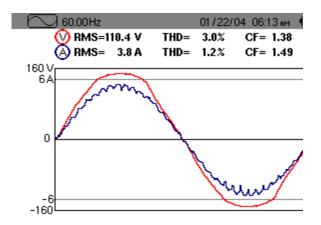

As it is obvious, the grid-connected PUC5 is operating in unity power factor and injecting active power to the grid. The grid-connected controller is working acceptably in making the current waveform in phase with ac voltage waveform.

## IEEE TRANSACTIONS ON INDUSTRIAL INFORMATICS

Moreover, the proposed sensor-less self-voltage-balancing method operates significantly perfect in regulating the capacitor voltage at desired level while encountering any kind of changes in the system and produces five-level voltage at the output of the inverter. Due to generating 5-level voltage waveform at the output of grid-connected PUC5 inverter, the injecting current through grid would have lower harmonic components without using any extra filters that enlarge the inverter package. Fig. 13 illustrates the current THD which is too much lower than the acceptable amount in standards.

Fig. 10: DC source voltage changes and capacitor voltage is tracking the reference value

Fig. 11: switches gate pulses

Fig. 12: grid-connected PUC5 with change in current reference amplitude

Fig. 13: THD, and Crest factor computation of injected grid current

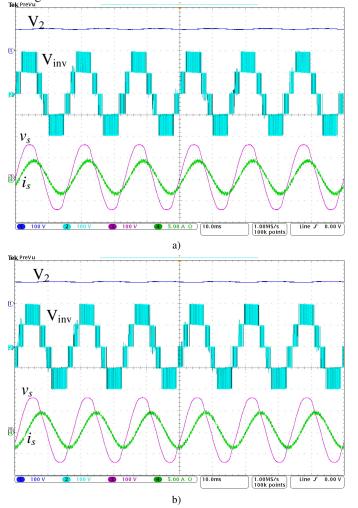

Final tests have been performed to exchange reactive power with the grid while injecting reduced amount of active power. Therefore, two different PFs of 0.86 and 0.5 have been selected and associated displacement angles are  $30^{\circ}$  and  $60^{\circ}$ ,

#### IEEE TRANSACTIONS ON INDUSTRIAL INFORMATICS

respectively as depicted in Fig 14 which shows the phase shift between grid voltage and current. In both cases  $(30^\circ \& 60^\circ)$  phase shift) the capacitor voltage is regulated at desired level, whereas inverter output waveform contains five identical voltage levels.

Fig. 14: PUC5 inverter operation at different power factors a) PF = 0.86,  $\theta = 30^{\circ}$  b) PF = 0.86,  $\theta = 60^{\circ}$

7-level waveform has been replaced by 5-level operation containing equal harmonic contents while a significant simplicity has been obtained on the controller with PWM switching technique useful for various industrial applications. In the PUC5 converter, due to accurate voltage balancing process, the output voltage waveform shows a good symmetry in positive and negative half cycles that makes its THD smaller.

#### VI. CONCLUSION

The PUC5 inverter has been proposed in this paper while the capacitor voltage is balanced without involving any external controller and voltage feedback sensors. The proposed sensor-less voltage controller has been integrated into switching technique to work as open-loop system with reliable results. Moreover, another controller has been designed for the PUC5 inverter to work as unity power factor grid-connected inverter. Low harmonics components in both voltage and current waveforms generated by PUC5, no need to bulky output filters, reliable and good dynamic performance in variable conditions (including change in DC source, load, power amount injected to the grid), requiring no sensor in stand-alone mode. voltage/current low manufacturing costs and miniaturized package due to using less components and etc are interesting advantages of the introduced PUC5 topology which have been proved by experimental results in both stand-alone and grid-connected modes. The presented PUC5 inverter can be a challenging candidate for conventional photovoltaic application inverters.

#### REFERENCES

- H. Abu-Rub, M. Malinowski, and K. Al-Haddad, Power electronics for renewable energy systems, transportation and industrial applications: John Wiley & Sons, 2014.

- [2] L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo, and M. A. M. Prats, "The age of multilevel converters arrives," *IEEE Ind. Electron. Mag.*, vol. 2, no. 2, pp. 28-39, 2008.

- [3] C. Cecati, F. Ciancetta, and P. Siano, "A multilevel inverter for photovoltaic systems with fuzzy logic control," *IEEE Trans. Ind. Electron.*, vol. 57, no. 12, pp. 4115-4125, 2010.

- [4] M. Seyedmahmoudian, S. Mekhilef, R. Rahmani, R. Yusof, and E. T. Renani, "Analytical modeling of partially shaded photovoltaic systems," *Energies*, vol. 6, no. 1, pp. 128-144, 2013.

- [5] H. Mortazavi, H. Mehrjerdi, M. Saad, S. Lefebvre, D. Asber, and L. Lenoir, "A Monitoring Technique for Reversed Power Flow Detection With High PV Penetration Level," *IEEE Trans. Smart Grid*, vol. 6, no. 5, pp. 2221-2232, 2015.

- [6] V. Biagini, P. Zanchetta, M. Odavic, M. Sumner, and M. Degano, "Control and modulation of a multilevel active filtering solution for variable-speed constant-frequency more-electric aircraft grids," *IEEE Trans. Ind. Informat.*, vol. 9, no. 2, pp. 600-608, 2013.

- [7] K. Gupta and S. Jain, "Topology for multilevel inverters to attain maximum number of levels from given DC sources," *IET Power Electron.*, vol. 5, no. 4, pp. 435-446, 2012.

- [8] M. F. Kangarlu and E. Babaei, "A Generalized Cascaded Multilevel Inverter Using Series Connection of Submultilevel Inverters," *IEEE Trans. Power Electron.*, vol. 28, no. 2, p. 625, 2013.

- [9] M. Mobarrez, M. Kashani, S. Bhattacharya, and R. Adapa, "Comparative study of DC circuit breakers using realtime simulations," in *IECON 2014-40th Annual Conference of the IEEE Industrial Electronics Society*, 2014, pp. 3736-3742.

- [10] H. Vahedi, K. Al-Haddad, Y. Ounejjar, and K. Addoweesh, "Crossover Switches Cell (CSC): A New Multilevel Inverter Topology with Maximum Voltage Levels and Minimum DC Sources," in *IECON 2013-39th Annual Conference on IEEE Industrial Electronics Society*, Austria, 2013, pp. 54-59.

- [11] Z. Li, P. Wang, Y. Li, and F. Gao, "A Novel Single-Phase Five-Level Inverter With Coupled Inductors," *IEEE Trans. Power Electron.*, vol. 27, no. 6, pp. 2716-2725, 2012.

- [12] H. Vahedi, S. Rahmani, and K. Al-Haddad, "Pinned Mid-Points Multilevel Inverter (PMP): Three-Phase Topology with High Voltage Levels and One Bidirectional Switch," in *IECON 2013-39th Annual Conference on IEEE Industrial Electronics Society*, Austria, 2013, pp. 100-105.

- [13] P. Roshankumar, P. Rajeevan, K. Mathew, K. Gopakumar, J. I. Leon, and L. G. Franquelo, "A Five-Level Inverter Topology with Single-DC Supply by Cascading a Flying Capacitor Inverter and an H-Bridge," *IEEE Trans. Power Electron.*, vol. 27, no. 8, pp. 3505-3512, 2012.

- [14] S. Daher, J. Schmid, and F. L. Antunes, "Multilevel inverter topologies for stand-alone PV systems," *IEEE Trans. Ind. Electron.*, vol. 55, no. 7, pp. 2703-2712, 2008.

- [15] H. Vahedi, K. Al-Haddad, P.-A. Labbe, and S. Rahmani, "Cascaded Multilevel Inverter with Multicarrier PWM Technique and Voltage Balancing Feature," in *ISIE 2014-23rd IEEE International Symposium on Industrial Electronics*, Turkey, 2014, pp. 2151-2156.

- [16] M. Sharifzadeh, H. Vahedi, A. Sheikholeslami, P.-A. Labbé, and K. Al-Haddad, "Hybrid SHM-SHE Modulation Technique for Four-Leg

#### IEEE TRANSACTIONS ON INDUSTRIAL INFORMATICS

NPC Inverter with DC Capacitors Self-Voltage-Balancing," *IEEE Trans. Ind. Electron.*, vol. 62, no. 8, pp. 4890-4899, 2015.

- [17] Y. Hinago and H. Koizumi, "A single-phase multilevel inverter using switched series/parallel dc voltage sources," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2643-2650, 2010.

- [18] H. Vahedi, K. Al-Haddad, and H. Y. Kanaan, "A New Voltage Balancing Controller Applied on 7-Level PUC Inverter," in *IECON* 2014-40th Annual Conference on *IEEE Industrial Electronics* Society, USA, 2014, pp. 5082-5087.

- [19] Y. Zhang, G. P. Adam, T. C. Lim, S. J. Finney, and B. W. Williams, "Hybrid multilevel converter: Capacitor voltage balancing limits and its extension," *IEEE Trans. Ind. Informat.*, vol. 9, no. 4, pp. 2063-2073, 2013.

- [20] K. Al-Haddad, Y. Ounejjar, and L. A. Gregoire, "Multilevel Electric Power Converter," US Patent 20110280052, Nov 2011.

- [21] Y. Ounejjar, K. Al-Haddad, and L. A. Grégoire, "Packed U cells multilevel converter topology: theoretical study and experimental validation," *IEEE Trans. Ind. Electron.*, vol. 58, no. 4, pp. 1294-1306, 2011.

- [22] H. Vahedi and K. Al-Haddad, "Real-Time Implementation of a Packed U-Cell Seven-Level Inverter with Low Switching Frequency Voltage Regulator," *IEEE Trans. Power Electron.*, 2015.

- [23] Y. Ounejjar, K. Al-Haddad, and L. A. Dessaint, "A Novel Six-Band Hysteresis Control for the Packed U Cells Seven-Level Converter: Experimental Validation," *IEEE Trans. Ind. Electron.*, vol. 59, no. 10, pp. 3808-3816, 2012.

- [24] E. Lupon, S. Busquets-Monge, and J. Nicolas-Apruzzese, "FPGA Implementation of a PWM for a Three-Phase DC–AC Multilevel Active-Clamped Converter," *IEEE Trans. Ind. Informat.*, vol. 10, no. 2, pp. 1296-1306, 2014.

- [25] H. Vahedi, A. Chandra, and K. Al-Haddad, "Five-Level Reduced-Switch-Count Boost PFC Rectifier with Multicarrier PWM," in *ECCE 2015-Energy Conversion Congress & Exposition*, Canada, 2015, pp. 2413-2420.

- [26] H. Hafezi, E. Akpinar, and A. Balikci, "Cascade PI controller for single-phase STATCOM," in 16th International Power Electronics and Motion Control Conference and Exposition (PEMC), 2014, pp. 88-93.

- [27] R. Teodorescu, F. Blaabjerg, M. Liserre, and P. C. Loh, "Proportional-resonant controllers and filters for grid-connected voltage-source converters," *IEE Proc. Electric Power Applications*, vol. 153, no. 5, pp. 750-762, 2006.

- [28] M. Saeedifard, R. Iravani, and J. Pou, "A space vector modulation strategy for a back-to-back five-level HVDC converter system," *IEEE Trans. Ind. Electron.*, vol. 56, no. 2, pp. 452-466, 2009.

- [29] J. Rodriguez, S. Bernet, P. K. Steimer, and I. E. Lizama, "A survey on neutral-point-clamped inverters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2219-2230, 2010.

- [30] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Perez, "A survey on cascaded multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2197-2206, 2010.

- [31] M. F. Escalante, J. C. Vannier, and A. Arzandé, "Flying capacitor multilevel inverters and DTC motor drive applications," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 809-815, 2002.

- [32] W. Wu, Y. He, T. Tang, and F. Blaabjerg, "A new design method for the passive damped LCL and LLCL filter-based single-phase gridtied inverter," *IEEE Trans. Ind. Electron.*, vol. 60, no. 10, pp. 4339-4350, 2013.

- [33] N. Vázquez, J. Villegas-Saucillo, C. Hernández, E. Rodríguez, and J. Arau, "Two-stage uninterruptible power supply with high power factor," *IEEE Trans. Ind. Electron.*, vol. 55, no. 8, pp. 2954-2962, 2008.

Hani Vahedi (S'10) was born in Sari, IRAN, in 1986. He received his B.Sc. and M.Sc. degrees both in electrical engineering from K. N. Toosi University of Technology (KNTU), Tehran, IRAN in 2008 and Babol University of Technology, Babol, IRAN in 2011, respectively.

He is currently pursuing his PhD at the École de Technologie Superieure (ÉTS), University of Quebec, in Montreal, Canada, as a member of Groupe de

Recherche en Électronique de Puissance et Commande Industrielle (GRÉPCI). His research interests include power electronics multilevel converters topology, control and modulation techniques, power quality, active power filter, and their applications into smart grid, renewable energy conversion, UPS, battery chargers and electric vehicles.

**Philippe-Alexandre Labbé** was born in Levis, Quebec, Canada. He is currently finishing his bachelor degree in electrical engineering at the École de Technologie Superieure (ÉTS), University of Quebec, in Montreal, Canada and will be pursuing his study as a graduate student in summer 2015 in the Groupe de Recherche en Électronique de Puissance et Commande Industrielle (GRÉPCI). His research efforts are presently concentrated on GaN device

modelling, printed circuit board analysis and multilevel converter control techniques in the application of motor drive, smart grid, battery charger and power hardware in the loop (Power HIL).

Kamal Al-Haddad (S'82-M'88-SM'92-F'07) received the B.Sc.A. and M.Sc.A. degrees from the University of Québec à Trois-Rivières, Canada, in 1982 and 1984, respectively, and the Ph.D. degree from the Institute National Polythechnique, Toulouse, France, in 1988. Since June 1990, he has been a Professor with the Electrical Engineering Department, École de Technologie Supérieure (ETS), Montreal, QC, where he has been the holder of the Canada

Research Chair in Electric Energy Conversion and Power Electronics since 2002. He has supervised more than 100 Ph.D. and M.Sc.A. students working in the field of power electronics. He is a Consultant and has established very solid link with many Canadian industries working in the field of power electronics, electric transportation, aeronautics, and telecommunications. He has coauthored more than 400 transactions and conference papers. His fields of interest are in high efficient static power converters, harmonics and reactive power control using hybrid filters, switch mode and resonant converters including the modeling, control, and development of prototypes for various industrial applications in electric traction, renewable energy, power supplies for drives, telecommunication, etc. Prof. Al-Haddad is a fellow member of the Canadian Academy of Engineering. He is IEEE IES President Elect 2014-2015, Associate editor of the Transactions on Industrial Informatics, IES Distinguished Lecturer and recipient of the Dr.-Ing. Eugene Mittelmann Achievement Award.