Received 11 March 2025, accepted 26 April 2025, date of publication 30 April 2025, date of current version 9 May 2025.

Digital Object Identifier 10.1109/ACCESS.2025.3566015

# **Z Packed U-Cell Modular Multilevel Converter for STATCOM Applications**

SANDY ATANALIAN<sup>®</sup><sup>1</sup>, (Graduate Student Member, IEEE), FADIA SEBAALY<sup>®</sup><sup>2</sup>, (Senior Member, IEEE), RAWAD ZGHEIB<sup>®</sup><sup>3</sup>, (Member, IEEE), AND KAMAL AL-HADDAD<sup>®</sup><sup>1</sup>, (Life Fellow, IEEE)

<sup>1</sup>Groupe de Recherche en Électronique de Puissance et Commandes Industrielles, École de Technologie Supérieure, Montreal, QC H3C 1K3, Canada <sup>2</sup>Centre de Recherche d'Hydro-Québec (IREQ), Hydro-Québec, Varennes, QC J3X 1S1, Canada

<sup>3</sup>G&W Electric Company, Bolingbrook, IL 60440, USA

Corresponding author: Sandy Atanalian (sandy.atanalian.1@ens.etsmtl.ca)

This work was supported by Canada Research Chair in Electrical Energy Conversion and in Power Electronics at École de Technologie Supérieure.

**ABSTRACT** The Modular Multilevel Converter (MMC) is a promising topology for STATCOM applications due to its key features, such as modularity, scalability, and reduced harmonic content. Increasing the number of voltage levels in MMC reduces harmonics but simultaneously increases the number of submodules (SMs) per arm, leading to larger sizes and higher costs, which presents a challenge. To address this, this article introduces a novel 17-level MMC-STATCOM based on the Z Packed U-Cell (ZPUC) converter as its SM, which enables the generation of more voltage levels with fewer components and reduced harmonic content, offering significant advantages in terms of size and cost. Given the complex structure of the proposed converter and the associated challenges in building a physical prototype, real-time (RT) simulation using FPGA technology is employed for validation. The key contributions include integrating the ZPUC-SM into a three-phase STATCOM for the first time and adapting the converter model and its control system to RT tools, including RT-LAB with an electric hardware solver for FPGA execution. In addition, capacitor voltage balancing and energy sorting algorithms are integrated within Phase-Shift Pulse Width Modulation, eliminating the need for an additional controller while maintaining the floating capacitors of ZPUC-SMs balanced and regulated. The specifications of the proposed converter are defined, the mathematical model and control system are derived, and a real-time implementation based on CPU and FPGA execution is built to verify the scheme. The obtained RT simulation results provide practical evidence confirming the effective operation of the proposed scheme in VAR compensation mode.

**INDEX TERMS** Electric hardware solver, modular multilevel converter, real-time implementation, RT-LAB, STATCOM, submodule, Z Packed U-Cell converter.

## I. INTRODUCTION

Nowadays, medium-voltage distribution systems face a surge in non-linear and unbalanced loads, primarily from industrial sources. These loads create power quality problems, such as harmonic distortion, low power factor, and uncontrollable reactive power, resulting in disturbances in the operation of the electrical system [1]. To ensure reliable operation, it is crucial to address these disturbances promptly. The

The associate editor coordinating the review of this manuscript and approving it for publication was Sunil Kumar Dube.

static synchronous compensator (STATCOM) emerges as a viable solution, offering effective reactive power compensation and voltage regulation, thereby enhancing power system performance [2], [3], [4].

Voltage Source Converters (VSCs) are considered essential among various types of converters. Two-level VSCs (2L-VSCs) are widely used in industrial applications due to their simple architecture and ease of control. However, implementing a practical STATCOM based on 2L-VSCs necessitates the use of line-frequency transformers, resulting in compensators that are bulky, heavy, and costly. High

switching losses and increased harmonic distortion necessitate extensive filtering, which impacts overall efficiency and system complexity. The limited voltage capability and poor scalability pose a challenge to their application in high-power scenarios. These limitations underscore the preference for multi-level converters (MLCs) in modern STATCOM designs, given their superior performance and scalability [5], [6].

STATCOMs based on MLCS have been extensively studied and employed due to their enhanced power ratings, improved power quality, lower harmonic distortion, and the ability to function without the need for bulky line-frequency transformers, making them suitable for medium- and highvoltage applications [5], [7]. Among the various MLC topologies, Flying Capacitor (FC), Neutral Point Clamped (NPC), and Cascaded H-Bridge (CHB) are prominent representatives [8], [9], [10]. The major drawback of the FC topology is the high expense associated with flying capacitors, particularly at low carrier frequencies. Additionally, they are not suitable for applications requiring pure 90° leading or lagging currents [11]. The NPC topology requires an additional voltage balancing circuit to manage the flying capacitors, and both FC and NPC topologies necessitate an increase in component count (capacitors, and clamping diodes) as the voltage levels increase [12]. The CHB topology remains one of the most suitable candidates for high-power reactive power compensation applications. However, CHB converters cannot operate continuously under unbalanced systems unless supplied by separate DC voltage sources. These sources are typically fed through multi-winding transformers, which reintroduce similar issues associated with line frequencies [13], [14].

Among the MLC topologies, Modular Multilevel Converter (MMC) is a promising topology for the next generation of converters for medium-/high voltage applications. Throughout the literature, MMCs have been employed in different applications such as Offshore wind Turbines [15], STATCOMS [16], Photovoltaic Systems [17], and Electric Vehicles [18]. They are characterized by various features such as reduced harmonic content, modularity, scalability, and easy expansion to a higher range of voltage levels [2], [4], [19]. Despite all the advantages of MMC for STATCOM applications, the implementation of this converter is still expensive due to the need for various submodules (SMs) per arm to generate a higher number of voltage levels. Thus, the improvement of the efficiency and the reliability of the converter is mandatory to reduce the operational costs and enable expanding the employment of MMC in the industrial sector and targeting various applications [4]. Additionally, the design of the MMC structure, which is inherently complex, is challenging, and depends on various factors such as the number of SM units per arm, the required number of voltage levels, the rating of semiconductor switches, and the design of SM capacitance [19], [20]. Different efforts have been presented in the literature to improve converter efficiency.

These efforts focused on SM design [4], circulating current control reduction/suppression that reduces power losses in the converter [20], and modulation techniques such as the nearest level modulation (NLM) [20] and the PS-PWM [21]. The switching losses of the converter can be improved by the selection of the SM topology [22], the use of wide-bandgap devices [23], and by the use of thyristor/diode bypassed SM [24].

In MMC, harmonic content could be further reduced by increasing the number of SMs/arms which in turn increases the number of generated voltage levels. However, this enhancement comes at the expense of a larger size and higher costs for the converter. Several SM topologies have been developed by researchers to enhance the performance of MMC. The topologies are classified based on various characteristics such as output voltage levels, SM polarity (uni-/bipolar), number of components per SM, and DC fault handling capability (DFH) [25], [26], [27]. The most common configurations are the Half-Bridge (HB) and the Full-Bridge (FB) [28], which both generate only 2L-voltages at their outputs. HB-SM has a very simple configuration and was initially employed in early MMC implementation [29]. In contrast, the FB-SM, despite incurring twice the switching and conduction losses compared to HB-SM, offers the advantage of DFH capability. In [30], the unidirectional cell (U) was introduced. U-SM reduces the number of active switches by half compared to HB-SM but experiences higher losses due to the presence of a diode. Furthermore, Clamped Diode (CD), featuring DFH capability, was introduced in [31]. This topology consists of two consecutive HB-SMs with an additional IGBT switch and two single diodes, thereby increasing both the size and cost of the MMC configuration.

Different multilevel SM topologies have been proposed in the literature, including the three-level neutral point clamped converter (3L-NPC) [26] and the three-level Flying Capacitor converter (3L-FC) [32]. However, 3L-NPC suffers from uneven current sharing among switches, leading to increased conduction losses [33], meanwhile, the drawback of 3L-FC is the huge number of DC voltage sources [26]. Another multilevel topology, the 5L- cross connected cell (5L-CCC) [34], achieves a 5L- output, but presents a major challenge in balancing its two capacitors. In [35], 7L Packed U-Cell converter was employed in MMC configuration to obtain a higher number of generated voltage levels, however, the necessitates a complex voltage balancing algorithm to balance the floating capacitors of the topology. Lately, authors of [36], have introduced the 5L- Z Packed U-Cell (5L-ZPUC) for MMC applications. This topology generates 5L at its output without any additional voltage balancing controller while reducing the components count when compared with other conventional topologies such as the HB-SM. Z Packed U-Cell (ZPUC) converter offers increased voltage levels with fewer components, thereby enhancing cost-effectiveness [37]. The different SM topologies introduced in the literature are summarized in Table 1 and compared in terms of hardware and

**TABLE 1. Different SM topologies for MMC.**

| Type  | ]   | Hardware Perspective |       |        | Control Perspective |             |

|-------|-----|----------------------|-------|--------|---------------------|-------------|

| SM    | #of | #of                  | #of   | #of    | Arm                 | Unipolar,   |

|       | SM  | C                    | IGBTs | Diodes | Voltage             | Bipolar/    |

|       |     |                      |       |        | Levels              | Multilevel? |

| HB    | N   | N                    | 2*N   | 2*N    | N                   | unipolar/no |

| U     | N   | N                    | N     | 2*N    | N                   | unipolar/no |

| FB    | N   | N                    | 4*N   | 4*N    | N                   | bipolar/no  |

| DC    | N   | 2*N                  | 5*N   | 7*N    | 2*N                 | unipolar/no |

| 3L-   | N   | 2*N                  | 4*N   | 6*N    | 3*N                 | bipolar/yes |

| NPC   |     |                      |       |        |                     |             |

| 3L-FC | N   | 2*N                  | 4*N   | 4*N    | 3*N                 | bipolar/yes |

| 5L-   | N   | 2*N                  | 6*N   | 6*N    | 5*N                 | bipolar/yes |

| CCC   |     |                      |       |        |                     |             |

| 7L-   | N   | 2*N                  | 6*N   | 6*N    | 7*N                 | bipolar/yes |

| PUC   |     |                      |       |        |                     |             |

control perspectives. Using a multilevel topology for the SM increases the number of generated voltage levels in each arm.

Although MMC is a promising topology, validating its control and modulation techniques poses challenges, especially in the absence of a physical prototype. Therefore, real-time (RT) simulation emerges as a vital tool for verifying the performance of complex topologies and validating proposed modulation and control techniques [1], [27], [38].

However, the numerous components of MMC, along with its non-linear devices, pose significant numerical challenges for computation, necessitating iterative techniques for accurate simulations [39], [40], [41].

RT simulation of MMC can be implemented on various platforms including the central processing unit (CPU) and the field programmable gate array (FPGA) [41]. While CPU-based modeling provides flexibility and ease of implementation, the execution time for each node typically ranges in tens of microseconds, thus limiting system accuracy. FPGA technology in RT offers a superior alternative, enabling simulation times to be reduced to hundreds of nanoseconds. This makes FPGA the optimal solution for RT simulation of MMC, allowing for smaller time-steps, faster simulation speeds, and improved result accuracy [39], [40], [41].

Aiming at these problems, this article is devoted to proposing a promising 17L- ZPUC-MMC STATCOM. The contributions include testing the converter for a three-phase STATCOM application using a conventional controller and adapting the converter model and its control to real-time tools including RT-LAB with an electric hardware solver (eHS) for FPGA execution. The proposed approach offers several advantages including: 1) the generation of a higher number of voltage levels with fewer component counts as compared to Half-Bridge MMC [37]. 2) Integration of inherent capacitor voltage balancing (VB) and energy sorting (ES) algorithms within Phase-Shift Pulse Width Modulation (PS-PWM); eliminating the need for an additional controller. 3) Modeling and implementing the complex converter on a RT platform, thus fast and efficient RT results are obtained. The paper is divided as follows: a comprehensive presentation of the ZPUC converter operating as a single SM and in MMC, along with VB and ES algorithms, is provided in

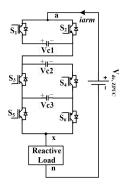

FIGURE 1. Z Packed U-Cell as a single inverter.

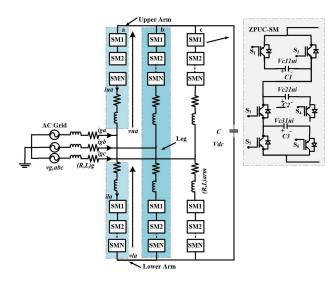

FIGURE 2. Proposed 17L- Z Packed U-Cell MMC STATCOM.

section II. The mathematical model and control are described in section III. Then, section IV illustrates the RT implementation and adaptation of the converter model and its proposed control system to real-time simulation tools using OP4510 Target Hardware, RT-LAB software, and electric Hardware Solver (eHS) for FPGA execution. The obtained RT simulation results are presented as proof of concept, validating the operation of the proposed system in VAR compensation mode in section V. ZPUC-MMC potential future works are discussed in section VI. And finally, to sum up, a conclusion is provided in section VII.

# **II. PROPOSED 17L-ZPUC-MMC STATCOM**

#### A. ZPUC SINGLE INVERTER

ZPUC was introduced as an inverter for both single-/three phase applications, as well as a submodule in MMC configurations. This converter uses a single DC source in both single-/three-phase systems. According to Fig. 1, t is built with six switches and three floating capacitors, where  $S_1$ ,  $S_3$ , and  $S_5$  are operated in a complementary manner to  $S_2$ ,  $S_4$ , and  $S_6$ , creating 8 (2^3) possible switching states. Maintaining balanced capacitor voltages is critical. Depending on the regulated values of the floating capacitors of ZPUC-SM, the

**TABLE 2.** Five levels ZPUC switching states.

| States | $S_1S_3S_5$ | $\mathbf{V}_{ax}$          | $V_{ax}$ (5L) |

|--------|-------------|----------------------------|---------------|

| 1      | 100         | $V_{c1} + V_{c2}$          | 4E            |

| 2      | 101         | $V_{c1} + V_{c2} - V_{c3}$ | 3E            |

| 3      | 110         | $V_{c1} + V_{c3}$          | 3E            |

| 4      | 111         | $V_{c1}$                   | 2E            |

| 5      | 000         | $V_{c2}$                   | 2E            |

| 6      | 001         | $V_{c2} - V_{c3}$          | E             |

| 7      | 010         | $V_{c3}$                   | E             |

| 8      | 011         | 0                          | 0             |

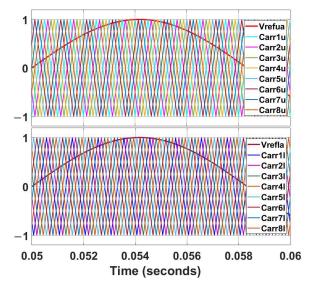

FIGURE 3. Reference voltage and carrier's waveforms in the upper and lower arm of phase a.

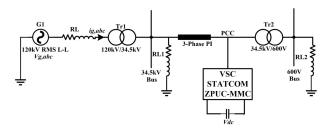

FIGURE 4. VSC ZPUC-MMC STATCOM connected in shunt with PCC.

output voltage can either be seven-level (7L-) or five-level (5L-). In this study, the 5L-ZPUC was selected due to its redundant switching states (see Table 2), which eliminates the need for an extra controller for capacitor voltage balancing, unlike the 7L-ZPUC. The voltage balancing (VB) for ZPUC capacitors is fully integrated within the modulation scheme.

The PS-PWM technique is employed for its various advantages including the uniform distribution of losses across all semiconductor switches, reduced Total Harmonics Distortion (THD), displacement of the harmonics further from the fundamental frequency, and enhancing the speed of integrated VB for auxiliary capacitors of ZPUC [21]. To achieve a 5L output at the ZPUC output, the capacitor voltages need to be set as per (1): capacitors  $C_1$  and  $C_2$  must hold 2E each, while capacitor  $C_3$  should maintain E. Here, 2E represents the total

DC voltage across the ZPUC-SM ( $V_{dc,ZPUC}$ ) [13]. As a first step, PS-PWM is applied. To generate L voltage levels, L-1 carriers, and one reference voltage are required. The carriers must be phase-shifted by an angle of  $360^{\circ}/(L-1)$ . In the case of a single ZPUC-SM, a 5L-output voltage is generated using four carriers that are phase-shifted by  $360^{\circ}/4$ . Selection between different redundant switching states is based on the conditions of capacitor voltages and arm current direction. For a detailed explanation of the integrated VB algorithm of ZPUC-SM within PS-PWM, please refer to [36].

$$v_{c1} = v_{c2} = 2E, v_{c3} = E$$

(1)

$$M_{phase} = 8N + 1 \tag{2}$$

$$M_{line} = 16N + 1 \tag{3}$$

#### B. ZPUC IN MMC-STATCOM

ZPUC-MMC STATCOM, as depicted in Fig. 2, comprises three legs, with each leg consisting of one upper and one lower arm. Each arm contains a total of N ZPUC-SMs, resulting in n ZPUC-SMs per leg. Upper and lower arm voltages constitute 4N + 1 levels arranged between 0 and 4NE in E steps, where 4NE is the total DC link voltage  $V_{dc}$ . Phase voltages are composed of  $M_{phase}$  levels as in (2), arranged between -2NE and 2NE in E/2 steps. Line-to-line voltages are composed of  $M_{line}$  levels as in (3), arranged between -4NE and 4NE in E/4 steps. In this work two ZPUC-SM are used in each arm (N = 2), hence a total of 4 ZPUC-SM per leg. Therefore, 9L- are generated in each of the upper and lower arms voltages, and 17L- are generated in each phase voltage. For the efficient and reliable operation of ZPUC-MMC STATCOM, the three floating capacitors of each ZPUC-SM should be balanced and regulated as in (3). The same integrated VB algorithm within PS-PWM of a single ZPUC-SM is applied for MMC application. However, when more than one ZPU-SM is employed per arm, an energy sorting (ES) algorithm is required to achieve energy balancing between ZPUC-SMs within one arm, and between ZPUC-SMs from different arms.

At first, to generate the 9L- upper and lower arms voltages, and based on part A of section II, 8 carriers (L-1) are required in each of the upper and lower arms. The upper arms carriers should be phase-shifted from the lower arms carriers by an angle of 22.5° (180°/8). Meanwhile, carries within the upper arms are phase-shifted at an angle of 45° (360°/8). Therefore, considering phase a, upper arm carriers should be placed at  $0^{\circ}$ ,  $45^{\circ}$ ,  $90^{\circ}$ ,  $135^{\circ}$ ,  $180^{\circ}$ ,  $225^{\circ}$ ,  $270^{\circ}$ , and 315°. Lower arm carries are placed at 22.5°, 67.5°, 112.5°, 157.5°, 202.5°, 247.5°, 292.5°, and 337.5°. The carriers in both the upper and lower arms of phase a, alongside the voltage reference, are depicted in Fig. 3. After applying PS-PWM, the next stage involves utilizing the ES algorithm to calculate the total energies of each ZPUC-SM across all arms and phases, as defined in (4). These energies are then sorted in ascending order within matrix I, detailed (5). For instance, in the upper arm of phase a, I (1) represents the ZPUC-SM with the lowest energy, while I (2) corresponds

**TABLE 3.** Comparison with conventional topologies.

| SM    | %    | SWL  | CL   | Compl | Cost | Control  |

|-------|------|------|------|-------|------|----------|

|       |      |      |      | exity |      |          |

| HB    | M    | L    | L    | L     | L    | Simple   |

| U     | M    | L    | L    | M     | M    | Simple   |

| FB    | M    | M    | M    | L     | L    | Simple   |

| DC    | Н    | L    | M    | Н     | M/H  | Moderate |

| 3L-   | Н    | Н    | Н    | M     | M    | Advanced |

| NPC   |      |      |      |       |      |          |

| 3L-FC | H    | Н    | Н    | M     | M    | Advanced |

| 5L-   | M    | L    | M    | Н     | Н    |          |

| CCC   |      |      |      |       |      | Complex  |

| 7L-   | Н    | L    | Very | Very  | Н    |          |

| PUC   |      |      | L    | H     |      | Complex  |

| 5L-   | Very | Very | Very | M     | M    | Moderate |

| ZPUC  | H    | L    | L    |       |      |          |

to the ZPUC-SM with the highest energy. Subsequently, the selection of optimal redundant switching states is based on the current direction in each arm and the conditions of capacitor voltages, guided by the factors outlined in [42]. A detailed description of the integrated VB algorithm along with the ES algorithm is beyond the scope of this article. For a comprehensive explanation of the VB and ES algorithms, as well as the conditions governing capacitor voltages and arm current directions in generating the various voltage levels, please refer to [36], [42].

$$E_i = \sum_{i=1}^{N} Vc_{ij}^2; j = 1, 2, 3$$

(4)

$$I = sort(E_i) \tag{5}$$

# C. COMPARISON WITH OTHER CONVENTIONAL SM TOPOLOGIES

This section compares ZPUC with other topologies based on factors like switching losses, conduction losses, capacitor voltage ripple, efficiency, and complexity. Table 3 Presents a comparison with commonly used topologies. Since HB-SM was the first SM topology proposed for the MMC, all comparisons in the table are made with HB-SM as the baseline [43], [44], [45]. L, M, and H denote low, moderate, and high, while SWL and CL denote switching losses, and conduction losses, respectively.

The trade-off between efficiency, complexity, and cost. is acknowledged. While higher-level topologies offer better performance, they also increase complexity and cost. The choice of SM topology depends on application-specific factors such as voltage level, power rating, efficiency, and cost constraints. In this context, the comparison is between a multilevel SM topology and the HB-SM. HB-SM, consisting of only two switches, results in moderate switching and conduction losses as current flows through just two devices. Despite its simplicity, it lacks redundancy, and the capacitor voltage ripple is moderate, as the DC link voltage in the MMC is divided across a single capacitor within each HB-SM. In contrast, a multilevel SM topology increases the number of switches but introduces redundancy, which reduces switching losses by decreasing the number of switching events. Conduction losses are also minimized as the

TABLE 4. Comparison between HB-MMC and ZPUC-MMC.

| Symbol                  | HB-SM  | ZPUC-SM     |

|-------------------------|--------|-------------|

| DC Voltage              | 60kV   | 60kV        |

| AC Line-to-Line Voltage | 34.5kV | 34.5kV      |

| System frequency        | 60Hz   | 60Hz        |

| Switching Frequency     | 1000   | 1000        |

| Modulation Index        | 0.95   | 0.95        |

| Number of SM/arm        | 16     | 2           |

| Voltage Levels          | 17L-   | 17L-        |

| Number of switches/SM   | 2      | 6           |

| Number of C/SM          | 1      | 3           |

| Components/arm          | 48     | 18          |

| Components/topology     | 288    | 108         |

| Cells Capacitors        | 20mF   | 20mF        |

| V caps                  | 3.75kV | 15kV, 7.5kV |

| Switches V Ratings      | 5kV    | 15kV, 7.5kV |

| Ripple in Vcaps         | <5%    | <1%         |

current is distributed across multiple devices, improving overall efficiency [46].

Multilevel topologies, like ZPUC-SM, generate higher voltage levels with fewer SMs, reducing filtering needs and mitigating harmonics. The finer voltage resolution minimizes capacitor voltage ripple, improving overall efficiency. In MMCs, ZPUC-SM divides the DC link voltage equally between the upper and lower legs, reducing voltage ripple compared to other topologies, which apply the full DC link voltage to both legs. Listing the comparisons and features of ZPUC-SM highlights its suitability for high-power applications, improving performance in reactive power compensation for STATCOM applications.

# D. COMPARISON BETWEEN HB-SM AND ZPUC-SM FOR MMC AND JUSTIFICATION FOR SELECTING ZPUC OVER HB

Conventional MMC submodules, such as Half-Bridge (HB) and Full-Bridge (FB) have been the cornerstone of MMC design due to their simplicity, reliability, and straightforward control schemes. However, they often require numerous SMs to achieve high voltage levels, increasing system complexity and footprint. In contrast, ZPUC-SM introduces a more compact and efficient alternative by integrating multiple voltage levels within a single cell. This enhances voltage balancing, reduces the required number of SMs, the overall size and cost of the MMC, and offers superior redundancy. Table 4 compares HB-SM and ZPUC-SM for MMC STATCOM applications under identical operating conditions [36], [37].

ZPUC-SM outperforms the HB-SM by generating more voltage levels with fewer SMs per arm. For example, to generate 17 levels (17L-), the HB-MMC requires 16 HB-SMs per arm, resulting in 32 switches per arm (each HB-SM consists of two switches). In contrast, the ZPUC-MMC needs only two ZPUC-SMs per arm, using just 12 switches per arm (each ZPUC-SM consists of six switches). This reduction in the number of SMs lowers the switch count and minimizes switching and conduction losses, thereby improving efficiency and reliability.

In terms of voltage control, the HB-SM provides only two voltage levels per SM (positive or zero), leading to higher voltage ripples and more filtering requirements to maintain quality. In contrast, the ZPUC-SM offers five voltage levels per SM, enabling smoother voltage control, better resolution, and reduced harmonic distortion. ZPUC-SM also balances output voltage more effectively at lower switching frequencies, reducing losses and boosting efficiency.

Additionally, the ZPUC topology integrates well with the Phase-Shift Pulse Width Modulation (PS-PWM) control method, eliminating complex balancing algorithms, and making it ideal for medium/high-voltage applications like STATCOMs.

In a MMC with HB-SM, (i.e. MMC operates as a grid-connected inverter) the total DC link voltage of the MMC converter is applied to both the upper and lower legs of the converter. However, with ZPUC-SM, the DC link voltage is equally split between the upper and lower legs of each phase, resulting in a lower voltage ripple per SM and reduced component stress.

ZPUC-SM was chosen for its ability to generate higher voltage levels with fewer components, reducing switching and conduction losses compared to HB-SM. The choice supports a more efficient, cost-effective solution, simplifying the design while meeting the performance needs of the MMC STATCOM application. ZPUC-SM for MMC enhances performance, reduces component stress, and improves efficiency, making it ideal for applications requiring high-quality output with minimal distortion.

#### III. MODELING AND CONTROL OF ZPUC-MMC STATCOM

# A. MATHEMATICAL MODEL AND GRID-CURRENT CONTROL

ZPUC-MMC STATCOM is implemented based on a voltage source converter (VSC) using a constant DC source represented by a DC link capacitor. The STATCOM is connected in shunt at the Point of Common Coupling (PCC) as shown in Fig. 4. A Switching modeling technique is adopted to extract the mathematical model presented in (6) to design the appropriate control system [37]. All the SMs of one arm are considered as one equivalent voltage source ( $v_{ui}$ ,  $v_{li}$ ). Using Kirchhoff's voltage law, the AC side voltages equation yields in (6), where,  $v_{ui}$  and  $v_{li}$  are the upper and lower arm voltages in phase i,  $v_{gi}$  and  $i_{gi}$  are the grid voltage and current in phase i,  $L_{arm}$ ,  $R_{arm}$  are arm inductance and resistance respectively, and  $L_g$ ,  $R_g$  are grid inductance and resistance.  $R_{arm}$  and  $R_g$  are very small, and they could be eliminated in all equations.

$$v_i - L_{eq} \frac{di_{gi}}{dt} + v_{gi} = 0, i = a, b, c$$

(6)

$L_{eq} = \frac{L_{arm}}{2} + L_g$ , and  $v_i = \frac{v_{li} - v_{ui}}{2}$ , i = a, b, c

The aim is to use conventional controllers from existing literature to assess the functionality of a new application for ZPUC-MMC.

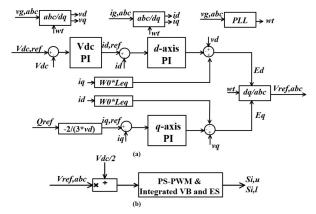

The control system, illustrated in Fig. 5 (a and b), employs decoupled PQ control in dq reference frame. It controls both

FIGURE 5. Control system of ZPUC-MMC STATCOM.

the d and q axis grid current separately by controlling the active power P and reactive power Q. Park transformation from abc reference frame to rotating dq0 reference frame is applied on (6), and the obtained d and q axis variables are as (7) and (8). Where,  $v_d$  and  $v_q$ ,  $i_d$  and  $i_q$ , and  $E_d$  and  $E_q$  are the grid voltages, grid currents, and output voltages of the controllers respectively on the d-axis and q-axis and  $w_0$  is the fundamental frequency.

$$E_d = v_d - L_{eq} \frac{di_d}{dt} + L_{eq} w_0 i_q \tag{7}$$

$$E_q = v_q - L_{eq} \frac{di_q}{dt} - L_{eq} w_0 i_d \tag{8}$$

Active and reactive power in dq0 reference frame is given below:

$$P = \frac{3}{2}(v_d i_d + v_q i_q)$$

(9)

$$Q = \frac{3}{2}(v_q i_d - v_d i_q) \tag{10}$$

Two PI controllers take action to regulate P to zero, and Q to follow reactive power reference  $Q_{ref}$ . The DC bus voltage is kept fixed throughout the d-axis external control loop. The command  $i_{d,ref}$  is obtained by comparing the actual DC bus voltage  $(V_{dc})$  with the reference DC bus voltage  $(V_{dc,ref})$  On the other hand, the command  $i_{q,ref}$ , is driven by the control objectives for the STATCOM, the provision of the reactive power support. The q-axis reference current is calculated as follows:  $i_{q,ref} = -2Q_{ref}/3v_d$ .

# **B. CIRCULATING CURRENT CONTROLLER**

In MMC, the instantaneous voltages among the three phases of the converter vary due to the voltage variation in the DC capacitors voltages of ZPUC and result in circulating current (CC) in each of the upper and lower arms of each leg. The relation between CC, output current (it is the grid current), and current in each arm is given as follows:

$$i_{ua} = i_{cca} + \frac{i_{ga}}{2} \tag{11}$$

$$i_{la} = i_{cca} - \frac{i_{ga}^2}{2}$$

(12)

**TABLE 5.** Upper and lower arms voltages and difference voltage.

| Sum of V <sub>u</sub> | Sum of V <sub>1</sub> ZPUC-MMC |            | $ m V_{diff}$ |

|-----------------------|--------------------------------|------------|---------------|

|                       | Output                         |            |               |

|                       |                                | Voltage    |               |

| 4NE                   | 0                              | 2NE        | 0             |

| 4NE                   | Е                              | (4N-1)E/2  | -E            |

| (4N-1)E               | 0                              | (4N-1)E/2  | E             |

| (4N-1)E               |                                | (2N-1)E    | 0             |

| :                     | :                              | :          | :             |

| :                     | :                              | :          | :             |

| E                     | 4NE                            | -(4N-1)E/2 | -E            |

| 0                     | 4NE                            | -2NE       | 0             |

where  $i_{ua}$  and  $i_{la}$  are the upper and lower arms currents in phase a, and  $i_{cca}$  is the circulating current in phase a. The CC caused by the variation in the instantaneous voltages among the three legs of the converter is an inherent phenomenon in MMC. Although CC does not affect AC-side grid voltages and grid currents, it is preferred to reduce it as much as possible for an efficient and reliable operation of the MMC [47]. The CC is composed of a DC term in addition to a double-line frequency component and can be expressed as in (13).

$$i_{cci} = \frac{I_{dc}}{3} + I_{2f}\sin(2w_0t + \varphi_0 + \varphi_i)$$

(13)

i=a,b,c, and  $\varphi_i=0,\frac{2\pi}{3}$ , and  $\frac{-2\pi}{3}$  respectively. where,  $i_{cci}$  is the circulating current in each phase i,  $I_{dc}$  is the total DC current, and  $I_{2f}$  is the peak value of the second-order frequency component,  $w_0$  is the fundamental frequency, and  $\varphi_0$  is the initial phase angle between the grid current and grid voltage. The available inductances in each arm of a MMC not only isolate upper and lower arms but also play a role in limiting the CC. Increasing  $L_{arm}$  can reduce the CC to a certain extent but at the expense of increasing the size, weight, and cost of the converter [48]. CC control has been addressed extensively in literature, and various control methods have been developed.

In ZPUC-MMC, the circulating current is automatically controlled by the integrated VB within the PS-PWM. The main equation that describes the dynamic equation of the CC is described in (14). The equation shows that the difference between DC and AC voltage results in the CC.

Therefore, to mitigate/reduce the CC, this voltage difference should be minimized. Table 5 presents the upper and lower arm voltages corresponding to the 8N + 1 states, along with the difference between DC and AC voltages (the circulating current). According to Table 5, this difference alternates between 0, E, and -E. Based on section II, part A, the total DC link voltage  $(V_{dc})$  is equal to 4NE, thus E is inversely proportional to N, the number of ZPUC-MS per arm. The expansion of the number of ZPUC-SM per arm (N)reduces the value of E, which describes the CC, that is the difference between DC and AC voltages.

$$v_{cci} = L_{arm} \frac{di_{cci}}{dt} + R_{arm} i_{cci}$$

(14)

where;  $v_{cci} = \frac{V_{dc}}{2} - (\frac{v_{li} + v_{ui}}{2})$ .

#### C. INTEGRATED VB AND ES ALGORITHMS WITH PWM

Various modulation techniques have been applied to MMCs such as the PS-PWM, the Level-Shift PWM, the Nearest Level Modulation (NLM), and the Space Vector Modulation (SVM). PS-PWM is applied to ZPUC-MMC due to its various advantages (listed in Section II, Part A). The reference voltage, previously obtained from grid-current control, is fed into the PWM blocks, which integrate both VB and ES algorithms to balance the floating capacitors of each ZPUC-SM in each arm and to balance energy within each leg and across the three legs (phases a, b, and c). Additionally, the output signals from the PWM blocks serve as the switching signals for the upper and lower arm switches in each phase i, where i=a,b, and c.

#### IV. REAL-TIME IMPLEMENTATION PLATFORM

### A. MAIN OBJECTIVES OF REAL-TIME SIMULATION

The main objective of RT simulation is to reproduce the output waveforms of a RT modeled plant that behaves identically to its physical prototype while maintaining high accuracy. To achieve RT simulation status, the execution or the computation of the modeled system should remain within the selected fixed time-step. This means that the execution time-step must be equal to or less than the selected fixed time-step. Otherwise, the execution time-step shrinks beyond the specified fixed time-step, leading to overruns, and RT simulation status is lost. The specified fixed time-step could be increased to eliminate overruns, but this affects the result's accuracy. To theoretically address the challenge of the execution time shrinking, two solutions are proposed. The first solution involves model simplification, where the complexity of the system model is reduced by using approximations or eliminating less critical components, helping to minimize the computational load and prevent the execution time-step from exceeding the selected fixed time-step. The second solution is parallel execution across multiple cores, which distributes the simulation tasks across the available cores on the realtime platform. This helps share the computational load and optimize execution time, though careful management of parallel execution is necessary to avoid synchronization issues. These approaches ensure that the system maintains real-time simulation status while preserving high accuracy in the simulation results.

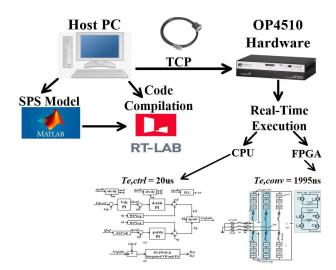

## B. REAL-TIME SIMULATION SOFTWARE AND HARDWARE

Due to the unavailability of a real physical small prototype, RT simulation is used to validate and verify the performance of the proposed converter and its control system under different modes of operation. Various RT simulation platforms are available today, such as Speedgoat, Typhoon HIL, and OPAL-RT. In this work, the OPAL-RT platform is used. Specialized hardware (Target) and software are required to perform RT execution. The OP4510 Target is employed in this work due to its availability in the GREPCI laboratory of the University. It offers a hybrid architecture with both

a powerful CPU and an FPGA for high-performance RT simulations. It integrates RT-LAB software and eFPGAsim RT platform. RT-LAB software is installed on a host PC at the GREPCI laboratory, and the host PC and the Target are connected via a Transmission Control Protocol (TCP), as illustrated in Fig. 6. In this article, a Model-in-the-Loop (MIL) or Control-in-the-Loop (CIL) simulation approach was used, where both the controller and the converter are modeled and executed using real-time hardware (Target). Specifically, the control system was executed on the CPU of the target, while the converter model was implemented and executed using the FPGA of the target. In industrial practice, alternative real-time simulation modes, such as Hardwarein-the-Loop (HIL) or Rapid-Control-Prototyping (RCP), can also be employed. In HIL mode, the controller is typically implemented on a Digital Signal Processor (DSP), while the converter model runs on the real-time target. In RCP mode, a physical prototype of the converter is used, which communicates with the real-time simulator for testing and validation.

RT-LAB software is fully compatible with MATLAB/ SIMULINK and provides an environment for testing and debugging complex power electronics converters. In the first step, the control system (VB and ES algorithms, and current control) is implemented in SIMULINK/MATLAB using the Sim Power Block Set (SPS). Then, through RT-LAB software, the control model in SPS is adapted for RT simulation by using specified blocks from the RT-LAB Library. RT-LAB software is based on a top-level SIMULINK model where only subsystems (Main SM, and Secondary SS) can be executed. Each subsystem requires one core from the Target for execution. It is important to note that one core of the Target is allocated by default for the Target processor.

Additionally, the electric Hardware Solver (eHS) block from RT-LAB software is inserted to model the ZPUC-MMC converter via the integrated schematic editor in eHS, which allows the design of ZPUC-MMC using switches, capacitors, inductors, and DC voltage source [49]. The Target hardware OP4510 typically consists of a high-performance processor (CPU) composed of four Intel Xeon 3.5GHZ processor cores, and one Xilinx Kintex-7 325T FPGA. The model subsystems executed using Target cores require a minimum time-step of 7µs. However, for models executed on FPGA chips, a minimum time-step of 250ns is necessary.

# C. REAL-TIME SIMULATION OF 17L-ZPUC-MMC STATCOM

Using only CPU-based RT simulation for complex power electronics systems, such as the ZPUC-MMC, is impractical. When utilizing only CPU-based RT simulation, the entire system (converter and control) is implemented in RT-LAB. The control (SM) is set as the main subsystem, while the converter (SS) is the secondary subsystem. In this setup, the system runs on just two cores of the Target machine. For instance, when employing one ZPUC-SM in a MMC, real-time status can only be obtained with a time-step of  $47\mu s$ , which is quite large and negatively impacts accuracy. Increasing further

FIGURE 6. Real-Time implementation of 17L-ZPUC-MMC.

the number of ZPU-SMs within the MMC arm results in more components, including switches and non-linear devices, which pose additional computational challenges and increase the CPU load. This can lead to the CPU becoming fully loaded, generating overruns.

When overruns occur, the executed time-step does not meet the specified time-step, causing results to be time-differed (offline) and not real-time. Increasing the specified time-step might be an alternative, but it comes at the expense of accuracy. Meanwhile, decomposing the system into additional subsystems to distribute execution across different available cores is challenging in terms of maintaining parallel execution. Therefore, for RT execution of ZPUC-MMC, both CPU and FPGA-based RT simulation should be employed. In this case, the control system is implemented on RT-LAB by transforming the control SPS model into a valid RT-LAB model using RT-LAB blocks library. The control system is then executed by the Target core. On the other hand, ZPUC-MMC STATCOM is implemented in the schematic editor, which is fully integrated within the eHS block of RT-LAB and then executed using the FPGA of the Target.

A significant contribution of the work is adapting the model of the converter for real-time simulation, ensuring verification and validation while achieving zero-overruns. Obtaining the model of the converter in the eHS block for FPGA execution required extensive tuning of the internal parameters of the converter switches presented in the schematic editor.

## **V. REAL-TIME SIMULATION RESULTS**

The proposed system along with its control system is implemented and executed on a RT simulation platform in a Model-in-the-Loop (MIL) mode of operation. The control system is executed with a time-step of  $20\mu s$  ( $T_{e,ctrl}$ ), and the converter itself is executed with a time-step of 1995ns ( $T_{e,conv}$ ). The setup of the RT platform shown in Fig. 6 is completed by connecting the host PC and the OPAL-RT target

**TABLE 6. System parameters.**

| Parameters                    | Symbols               | Values                         |

|-------------------------------|-----------------------|--------------------------------|

| RMS line-to-line Voltage      | $V_s$                 | 34.5kV                         |

| Grid Frequency                | $f_0$                 | 60Hz                           |

| DC Voltage Reference          | $V_{dc,ref}$          | $60 \mathrm{kV}$               |

| Reactive Power Range          | $Q_{ref}$             | -150/150Mvar                   |

| Grid Reactance and Resistance | $L_g$ , $R_g$         | $1$ mH, $0.1\Omega$            |

| Arm Inductance and Resistance | $L_{arm}$ , $R_{arm}$ | $0.5 \mathrm{mH}, 0.05 \Omega$ |

| Number of ZPUC-SM per arm     | N                     | 2                              |

| ZPUC Capacitors               | $C_1$ , $C_2$ , $C_3$ | 30mF                           |

| Switching Frequency           | $f_{sw}$              | 1000Hz                         |

Hardware (OP4510) via a Transmission Control Prototype (TCP). The target features 3.5GHz Intel Xeon four-core processors with Red Hat Linux Operating System and a powerful Xilinx Kintex-7 FPGA. The simulation parameters are outlined in Table 6. Assuming a balanced three-phase system, the results per phase 'a' will only be displayed and analyzed.

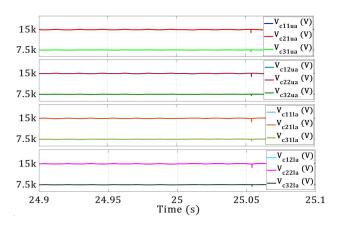

### A. BALANCED THREE-PHASE SYSTEMS

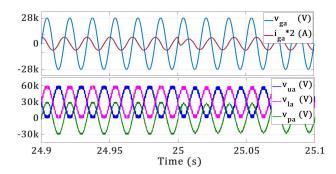

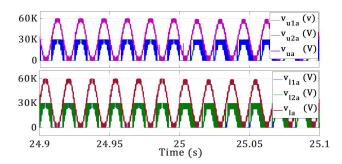

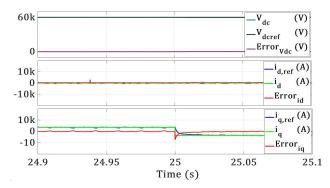

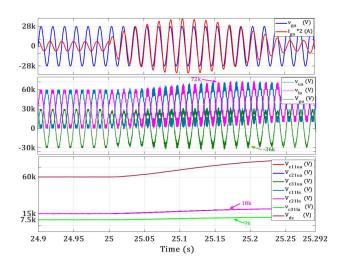

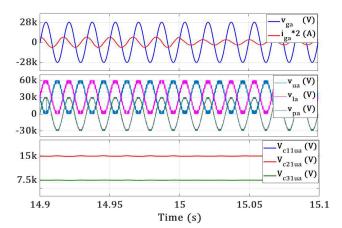

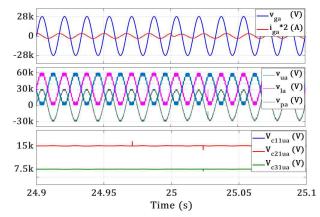

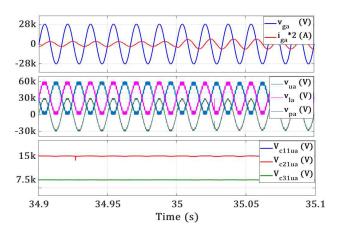

At t = 25s, the compensated reactive power shifts from -150 Mvar capacitive to 150 Mvar inductive. Consequently, the grid-side current changes from leading the grid voltage by 90° to lagging it by 90° as depicted in Fig. 7. Notably, throughout this transition, the current waveform maintains a perfect sinusoidal shape. According to Fig. 7, 17L-(8N + 1) phase voltage  $(v_{pa})$  is perfectly generated and arranged between  $-V_{dc}/2$  (-30kV) and  $V_{dc}/2$  (30kV) in E/2 steps (3.75kV). In addition, 9L- (4N + 1) upper and lower arm voltages  $(v_{ua}, v_{la})$  are quite generated and are arranged between 0 and 4NE (60kV) in E steps (7.5kV). These 9Lvoltages result from adding the 5L- voltages generated by each ZPUC-SM in each upper arm  $(v_{u1a}, v_{u2a})$  and lower arm  $(v_{l1a}, v_{l2a})$  as shown in Fig. 8. This shows the good dynamic performance of the proposed system through FPGA-based RT simulations. Also, the DC bus voltage remains constant with zero steady-state error as shown in Fig. 9, enabling uninterrupted converter operation. According to Fig. 10, the integrated VB and ES algorithms are perfectly achieved. The three capacitor voltages of each ZPUC-SM in each upper and lower arm of phase 'a' are very well balanced and regulated around desired values with a small voltage ripple. The voltages of capacitors  $C_1$  and  $C_2$  of each ZPUC-SM in each arm are equal to 2E (15kV), and the voltage of capacitor  $C_3$ is equal to E (7.5kV). Thus,  $v_{c1xja} = v_{c2xja} = 15$ kV, and  $v_{c3xia}$  =7.5kv, where; x = 1, 2 is the index of ZPUC-SM in each arm, and j = u, l is the index of each arm (upper, lower) in phase a.

# **B. DYNAMIC OPERATION**

To assess the dynamic performance of the proposed converter, tests were conducted under variations in the DC voltage reference and reactive power reference.

The first variation involves a step change of 20% in the DC voltage reference, applied at t = 25s, increasing  $V_{dcref}$

FIGURE 7. Grid voltage and current  $(v_{ga}, i_{ga})$ , 9L-upper and lower arm voltages  $(v_{ua}, v_{la})$ , and 17L- phase voltage  $(v_{pa})$  in phase a.

FIGURE 8. 5L- ZPUC-SMs voltages in upper and lower arm  $(v_{u1a}, v_{u2a}, v_{l1a}, v_{l2a})$ , and 9L- upper and lower arm voltages  $(v_{ua}, v_{la})$  in phase a.

FIGURE 9. DC bus voltage (V<sub>dc</sub>), and currents on the d and q axes.

from 60kV to 72kV. Additionally, at t = 25s, the compensated reactive power shifts from capacitive to inductive. The respective results are depicted in Fig. 11. It is clearly observed that the grid-current control remains robust against DC voltage variations: the current remains sinusoidal, leading the grid voltage by 90° before the step change (capacitive reactive power) and shifting to lagging the grid voltage by 90° after the step change (inductive reactive power). Similarly, 9L- voltages are generated in each of the upper and lower arms ( $v_{ua}$ ,  $v_{la}$ ), with 17L- voltages appearing in the phase voltage ( $v_{pa}$ ). However, these voltage levels adapt to the newly applied DC voltage value (72kV), validating the previously introduced formulas in (1), (2), and (3) in section II. Consequently, the upper and lower arm voltages are arranged between 0 and 4E (72kV), while the 17L- phase voltage varies between  $V_{dc}/2$ (36kV) and  $-V_{dc}/2$  (-36kV). Furthermore, the three capacitors of ZPUC-SM1 in both the upper and lower arms of the phase

FIGURE 10. Capacitor voltages of ZPUC-SMs in phase a.

FIGURE 11. Dynamic operation: DC voltage variation.

'a' maintain balance around their desired values according to the new DC voltage, validating the effectiveness of the voltage balancing and energy sorting algorithms integrated within the PS-PWM. Specifically,  $V_{c11ua}$ ,  $V_{c21ua}$ ,  $V_{c11la}$ , and  $v_{c21la}$  are balanced and regulated around 2E = 18kV, while  $V_{C31ua} = V_{c31la} = 9$ kV= E. The capacitor voltage ripple remains below 10%.

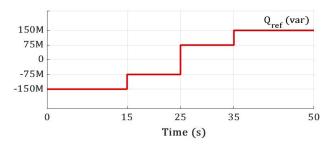

The second variation involves a step change in the reactive power reference over a time range of 50 seconds, aimed at ensuring the STATCOM operates efficiently across its full operating range, from -150 Mvar to +150 Mvar. The dynamic step change is illustrated in Fig. 12, with the corresponding real-time simulation results shown in Figs. 13, 14, and 15. Since each second in the real-time simulation corresponds to one second in the real world, and given the difficulty of testing the three different variations within the same time range (0s-50s), the results are divided into three time-slots: at t=15s, a step change is applied, reducing the reactive power reference from -150 Mvar into -75 Mvar. At t=25s, another step change occurs, shifting the reactive power reference from capacitive (-75 Mvar) to inductive (75Mvar). Finally, at t=35s, the inductive reactive power increases to 150 Mvar.

FIGURE 12. Dynamic operation: reactive power step variation.

FIGURE 13. Dynamic operation: -150Mvar to -75 Mvar.

FIGURE 14. Dynamic operation: -75 Mavr to +75 Mvar.

As shown in Fig. 13, the sinusoidal grid current consistently leads the grid voltage by  $90^{\circ}$ , but at t=15s, the current amplitude decreases due to the reduction of the reactive power reference to -75 Mvar. At t=25s, the current shifts from leading to lagging the grid voltage by  $90^{\circ}$ , as the reference changes from capacitive to inductive as described in Fig. 14. In Fig.15, the current continues lagging the grid voltage by  $90^{\circ}$ , but its amplitude increases as the reactive power reference is stepped from 75 Mvar to 150 Mvar.

In all cases, the same number of voltage levels (9L-) are generated in each of the upper and lower arms of phase a, and 17L- phase voltage is consistently generated. Additionally, the capacitors of each ZPUC-SM continue to balance around their regulated values, validating the robustness and

FIGURE 15. Dynamic operation: +75 Mvar to +150 Mvar.

effectiveness of the voltage balancing and energy sorting algorithms integrated within the PS-PWM.

## **VI. TOPOLOGY LIMITATIONS AND FUTURE WORK**

One potential advantage of the ZPUC-SM in MMC systems is its ability to boost voltage levels using fewer building blocks (SMs). It also has a simpler design due to the lower number of components, and it incorporates an automatic voltage balancing function achieved through a PS-PWM technique. However, one drawback of ZPUC-SM is that it operates with only one voltage polarity (unipolar) and switching devices cannot block DC fault currents. External DC circuit breakers are required. However, they are not as mature as AC circuit breakers and have some related losses, fault clearing time, and arcing time [50]. Therefore, for High-/Medium-Voltage Direct Current (HVDC and MVDC) MMC applications, using ZPUC is challenging due to the high probability of experiencing pole-to-pole or pole-to-ground faults. A DC fault is one of the severe faults that can occur in an MMC and has a significant impact on the grid. It is usually classified based on the distance between the fault and the DC connection point. A DC fault occurring 1 meter away from the DC connection point is considered the worst-case scenario for a converter. The switches will be subjected to high overcurrent that will propagate to the AC side if the fault is not isolated. To overcome this limitation, the authors are developing a new submodule design that combines the strengths of both ZPUC and Full-Bridge configurations. This hybrid design aims to include the capability to block DC faults.

Future work could focus on developing advanced control strategies, such as Model Predictive Control (MPC) or Adaptive Control, to further optimize the performance of MMC-based STATCOMs under dynamic conditions and varying grid scenarios. Another important research area involves improving component reliability, particularly capacitors and switches in submodules. Long-term reliability studies and improvements in power semiconductor technologies are essential for reducing maintenance costs and extending system lifespans.

In ZPUC-MMCs, circulating current control is inherently integrated with voltage balancing and modulation techniques. While arm inductors help to minimize CC, it cannot be totally eliminated. However, the presence of second-order harmonics within the CC can be addressed. This opens the door to a novel approach: exploring the application of external controllers, like those used in established MMC configurations such as the HB-MMC, to manage CC independently. Such an approach could potentially allow for its complete suppression [51].

#### VII. CONCLUSION

This work introduces a promising MMC-STATCOM based on ZPUC-SM, thoroughly exploring its adaptation for FPGAbased real-time simulation. The proposed ZPUC-MMC offers several advantages, including fewer components, lower cost, increased voltage levels, and highly accurate real-time simulation results, validating the converter's operation. The system operates in VAR compensation mode, using conventional controllers based on the decoupled dq reference frame for grid current internal loop regulation, and DC bus voltage external loop regulation. Despite these benefits, technical challenges remain, particularly in blocking DC faults and controlling circulating currents in MMCs. Future research will focus on developing a hybrid ZPUC design to address DC fault blocking and exploring advanced control techniques to fully mitigate circulating currents. Additionally, further investigation into integrating real-time hardware simulations with physical prototypes will be crucial for validating the proposed system in industrial applications.

# **REFERENCES**

- [1] S. Du and J. Liu, "A study on DC voltage control for chopper-cell-based modular multilevel converters in D-STATCOM application," *IEEE Trans. Power Del.*, vol. 28, no. 4, pp. 2030–2038, Oct. 2013, doi: 10.1109/TPWRD.2013.2246195.

- [2] X. Liu, J. Lv, C. Gao, Z. Chen, and S. Chen, "A novel STAT-COM based on diode-clamped modular multilevel converters," *IEEE Trans. Power Electron.*, vol. 32, no. 8, pp. 5964–5977, Aug. 2017, doi: 10.1109/TPEL.2016.2616495.

- [3] S. Sharma, S. Gupta, M. Zuhaib, V. Bhuria, H. Malik, A. Almutairi, A. Afthanorhan, and M. Asef Hossaini, "A comprehensive review on STATCOM: Paradigm of modeling, control, stability, optimal location, integration, application, and installation," *IEEE Access*, vol. 12, pp. 2701–2729, 2024, doi: 10.1109/ACCESS.2023.3345216.

- [4] R. O. de Sousa, A. F. Cupertino, L. M. F. Morais, H. A. Pereira, and R. Teodorescu, "Experimental validation and reliability analyses of minimum voltage control in modular multilevel converter-based STATCOM," *IEEE Trans. Ind. Electron.*, vol. 71, no. 7, pp. 6546–6555, Jul. 2024, doi: 10.1109/TIE.2023.3303634.

- [5] I. Harbi, J. Rodriguez, A. Poorfakhraei, H. Vahedi, M. Guse, M. Trabelsi, M. Abdelrahem, M. Ahmed, M. Fahad, C.-H. Lin, T. Wijekoon, W. Tian, M. L. Heldwein, and R. Kennel, "Common DC-link multilevel converters: Topologies, control and industrial applications," *IEEE Open J. Power Electron.*, vol. 4, pp. 512–538, 2023, doi: 10.1109/OJPEL.2023.3291662.

- [6] N. N. V. Surendra Babu and B. G. Fernandes, "Cascaded two-level inverter-based multilevel STATCOM for high-power applications," *IEEE Trans. Power Del.*, vol. 29, no. 3, pp. 993–1001, Jun. 2014, doi: 10.1109/TPWRD.2014.2305692.

- [7] J. Fang, F. Blaabjerg, S. Liu, and S. M. Goetz, "A review of multilevel converters with parallel connectivity," *IEEE Trans. Power Electron.*, vol. 36, no. 11, pp. 12468–12489, Nov. 2021, doi: 10.1109/TPEL.2021.3075211.

- [8] A. Shukla, A. Ghosh, and A. Joshi, "Hysteresis current control operation of flying capacitor multilevel inverter and its application in shunt compensation of distribution systems," *IEEE Trans. Power Del.*, vol. 22, no. 1, pp. 396–405, Jan. 2007, doi: 10.1109/TPWRD.2006.877100.

- [9] M. Saeedifard, H. Nikkhajoei, and R. Iravani, "A space vector modulated STATCOM based on a three-level neutral point clamped converter," *IEEE Trans. Power Del.*, vol. 22, no. 2, pp. 1029–1039, Apr. 2007, doi: 10.1109/TPWRD.2007.893448.

- [10] Y. Neyshabouri, K. K. Monfared, H. Iman-Eini, Q. Xiao, and M. Farhadi-Kangarlu, "Cascaded H-bridge based STATCOM with improved ride through capability of submodule failures," *IEEE Trans. Ind. Electron.*, vol. 69, no. 4, pp. 4034–4045, Apr. 2022, doi: 10.1109/TIE.2021.3071703.

- [11] K. Fujii and R. W. De Doncker, "Optimization of soft-switched flying capacitor multi-level converters applied to STATCOMs," in *Proc. Eur. Conf. Power Electron. Appl.*, Sep. 2007, pp. 1–10, doi: 10.1109/EPE.2007.4417402.

- [12] J. Zhou and P.-T. Cheng, "Modulation methods for 3L-NPC converter power loss management in STATCOM application," *IEEE Trans. Ind. Appl.*, vol. 55, no. 5, pp. 4965–4973, Sep. 2019, doi: 10.1109/TIA.2019.2924407.

- [13] G. Farivar, B. Hredzak, and V. G. Agelidis, "Decoupled control system for cascaded H-bridge multilevel converter based STATCOM," *IEEE Trans. Ind. Electron.*, vol. 63, no. 1, pp. 322–331, Jan. 2016, doi: 10.1109/TIE.2015.2472358.

- [14] X. Ge and F. Gao, "Flexible third harmonic voltage control of low capacitance cascaded H-Bridge STATCOM," *IEEE Trans. Power Electron.*, vol. 33, no. 3, pp. 1884–1889, Mar. 2018, doi: 10.1109/TPEL.2017.2738778.

- [15] S. Jiang, Y. Xin, G. Li, and L. Wang, "A novel DC fault ride-through method for wind farms connected to the grid through bipolar MMC-HVDC transmission," *IEEE Trans. Power Del.*, vol. 35, no. 6, pp. 2937–2950, Dec. 2020, doi: 10.1109/TPWRD.2020.2991722.

- [16] X. Yu, Y. Wei, and Q. Jiang, "STATCOM operation scheme of the CDSM-MMC during a pole-to-pole DC fault," *IEEE Trans. Power Del.*, vol. 31, no. 3, pp. 1150–1159, Jun. 2016, doi: 10.1109/TPWRD.2015.2464320.

- [17] J. Mei, B. Xiao, K. Shen, L. M. Tolbert, and J. Y. Zheng, "Modular multilevel inverter with new modulation method and its application to photovoltaic grid-connected generator," *IEEE Trans. Power Electron.*, vol. 28, no. 11, pp. 5063–5073, Nov. 2013, doi: 10.1109/TPEL.2013.22 43758.

- [18] D. Ronanki and S. S. Williamson, "Modular multilevel converters for transportation electrification: Challenges and opportunities," *IEEE Trans. Transport. Electrific.*, vol. 4, no. 2, pp. 399–407, Jun. 2018, doi: 10.1109/TTE.2018.2792330.

- [19] A. F. Cupertino, J. V. M. Farias, H. A. Pereira, S. I. Seleme, and R. Teodorescu, "Comparison of DSCC and SDBC modular multilevel converters for STATCOM application during negative sequence compensation," *IEEE Trans. Ind. Electron.*, vol. 66, no. 3, pp. 2302–2312, Mar. 2019, doi: 10.1109/TIE.2018.2811361.

- [20] S. Li, X. Wang, Z. Yao, T. Li, and Z. Peng, "Circulating current suppressing strategy for MMC-HVDC based on nonideal proportional resonant controllers under unbalanced grid conditions," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 387–397, Jan. 2015, doi: 10.1109/TPEL.2014.2329059.

- [21] S. Arazm, H. Vahedi, and K. Al-Haddad, "Generalized phase-shift pulse width modulation for multi-level converters," in *Proc. IEEE Electr. Power Energy Conf. (EPEC)*, Oct. 2018, pp. 1–6, doi: 10.1109/EPEC.2018.8598340.

- [22] T. Modeer, H.-P. Nee, and S. Norrga, "Loss comparison of different sub-module implementations for modular multilevel converters in HVDC applications," *EPE J.*, vol. 22, no. 3, pp. 32–38, Sep. 2012, doi: 10.1080/09398368.2012.11463829.

- [23] L. Wu, J. Qin, M. Saeedifard, O. Wasynczuk, and K. Shenai, "Efficiency evaluation of the modular multilevel converter based on Si and SiC switching devices for medium/high-voltage applications," *IEEE Trans. Electron Devices*, vol. 62, no. 2, pp. 286–293, Feb. 2015, doi: 10.1109/TED.2014.2375875.

- [24] P. D. Judge, M. M. C. Merlin, T. C. Green, D. R. Trainer, and K. Vershinin, "Thyristor/diode-bypassed submodule power groups for improved efficiency in modular multilevel converters," *IEEE Trans. Power Del.*, vol. 34, no. 1, pp. 84–94, Feb. 2019, doi: 10.1109/TPWRD.2018.28 43390.

- [25] S. Debnath, J. Qin, B. Bahrani, M. Saeedifard, and P. Barbosa, "Operation, control, and applications of the modular multilevel converter: A review," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 37–53, Jan. 2015, doi: 10.1109/TPEL.2014.2309937.

- [26] E. Solas, G. Abad, J. A. Barrena, S. Aurtenetxea, A. Cárcar, and L. Zajac, "Modular multilevel converter with different submodule concepts—Part I: Capacitor voltage balancing method," *IEEE Trans. Ind. Electron.*, vol. 60, no. 10, pp. 4525–4535, Oct. 2013, doi: 10.1109/TIE.2012.2210378.

- [27] Y. Jin, Q. Xiao, J. Pou, H. Jia, Y. Ji, R. Teodorescu, and F. Blaabjerg, "A novel fault-tolerant operation approach for the modular multilevel converter-based STATCOM with the enhanced operation capability," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 10, no. 5, pp. 5541–5552, Oct. 2022, doi: 10.1109/JESTPE.2022.3151911.

- [28] S. Ali, Z. Ling, K. Tian, and Z. Huang, "Recent advancements in sub-module topologies and applications of MMC," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 9, no. 3, pp. 3407–3435, Jun. 2021, doi: 10.1109/JESTPE.2020.2990689.

- [29] M. Glinka and R. Marquardt, "A new AC/AC-multilevel converter family applied to a single-phase converter," in *Proc. 5th Int. Conf. Power Electron. Drive Syst.*, Singapore, Nov. 2003, pp. 16–23, doi: 10.1109/PEDS.2003.1282669.

- [30] G. J. M. D. Sousa and M. L. Heldwein, "Modular multilevel converter based unidirectional medium/high voltage drive system," in *Proc. IECON-*39th Annu. Conf. IEEE Ind. Electron. Soc., Nov. 2013, pp. 1037–1042, doi: 10.1109/IECON.2013.6699276.

- [31] S. Cui, S. Kim, J.-J. Jung, and S.-K. Sul, "Principle, control and comparison of modular multilevel converters (MMCs) with DC short circuit fault ride-through capability," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, Mar. 2014, pp. 610–616, doi: 10.1109/APEC.2014.6803371.

- [32] V. Dargahi, A. K. Sadigh, M. Abarzadeh, S. Eskandari, and K. A. Corzine, "A new family of modular multilevel converter based on modified flying-capacitor multicell converters," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 138–147, Jan. 2015, doi: 10.1109/TPEL.2014.23 04964.

- [33] J. Rodriguez, S. Bernet, P. K. Steimer, and I. E. Lizama, "A survey on neutral-point-clamped inverters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2219–2230, Jul. 2010, doi: 10.1109/TIE.2009.2032430.

- [34] A. Nami, L. Wang, F. Dijkhuizen, and A. Shukla, "Five level cross connected cell for cascaded converters," in *Proc. 15th Eur. Conf. Power Electron. Appl. (EPE)*, Sep. 2013, pp. 1–9, doi: 10.1109/EPE.2013.66 31941.

- [35] M. Sleiman, H. F. Blanchette, K. Al-Haddad, L.-A. Grégoire, and H. Kanaan, "A new 7L-PUC multi-cells modular multilevel converter for AC-AC and AC-DC applications," in *Proc. IEEE Int. Conf. Ind. Technol. (ICIT)*, Mar. 2015, pp. 2514–2519, doi: 10.1109/ICIT.2015.71 25468.

- [36] S. Arazm and K. Al-Haddad, "ZPUC: A new configuration of single DC source for modular multilevel converter applications," *IEEE Open J. Ind. Electron. Soc.*, vol. 1, pp. 97–113, 2020, doi: 10.1109/OJIES.2020.2998694.

- [37] S. Atanalian, F. Sebaaly, S. Arazm, R. Zgheib, K. Al-Haddad, and H. Y. Kanaan, "Three-phase ZPUC-MMC grid connected converter," in *Proc. IECON-48th Annu. Conf. IEEE Ind. Electron. Soc.*, Oct. 2022, pp. 1–6, doi: 10.1109/IECON49645.2022.9968917.

- [38] M. D. Omar Faruque, T. Strasser, G. Lauss, V. Jalili-Marandi, P. Forsyth, C. Dufour, V. Dinavahi, A. Monti, P. Kotsampopoulos, J. A. Martinez, K. Strunz, M. Saeedifard, X. Wang, D. Shearer, and M. Paolone, "Realtime simulation technologies for power systems design, testing, and analysis," *IEEE Power Energy Technol. Syst. J.*, vol. 2, pp. 63–73, 2015, doi: 10.1109/JPETS.2015.2427370.

- [39] W. Li, L.-A. Gregoire, S. Souvanlasy, and J. Belanger, "An FPGA-based real-time simulator for HIL testing of modular multilevel converter controller," in *Proc. IEEE Energy Convers. Congr. Expo. (ECCE)*, Sep. 2014, pp. 2088–2094, doi: 10.1109/ECCE.2014.6953678.

- [40] H. Saad, T. Ould-Bachir, J. Mahseredjian, C. Dufour, S. Dennetière, and S. Nguefeu, "Real-time simulation of MMCs using CPU and FPGA," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 259–267, Jan. 2015, doi: 10.1109/TPEL.2013.2282600.

- [41] H. Pang, F. Zhang, H. Bao, G. Joós, W. Wang, W. Li, L.-A. Gregoire, and X. Zhai, "Simulation of modular multilevel converter and DC grids on FPGA with sub-microsecond time-step," in *Proc. IEEE Energy Convers. Congr. Expo. (ECCE)*, Cincinnati, OH, USA, Oct. 2017, pp. 2673–2678, doi: 10.1109/ECCE.2017.8096503.

- [42] S. Atanalian, F. Sebaaly, R. Zgheib, and K. Al-Haddad, "Voltage balancing and energy sorting of 17L-ZPUC-Based modular multilevel converter," in *Proc. IEEE Int. Conf. Ind. Technol. (ICIT)*, Orlando, FL, USA, Apr. 2023, pp. 1–4, doi: 10.1109/ICIT58465.2023.10143165.

- [43] P. Guicharrousse, Md. Rishad Ahmed, P. Wheeler, and P. Zanchetta, "New approach for comparing modular multilevel converter submodule losses considering IGBT and SiC MOSFET devices," in *Proc. IECON-*48th Annu. Conf. IEEE Ind. Electron. Soc., Oct. 2022, pp. 1–6, doi: 10.1109/IECON49645.2022.9968842.

- [44] M. Kurtoglu, A. O. Arslan, F. Eroglu, and A. M. Vural, "Comparison of different submodule topologies in modular multilevel converters," in *Proc.* 3rd Int. Symp. Multidisciplinary Stud. Innov. Technol. (ISMSIT). Turkey: IEEE, Oct. 2019, pp. 1–5, doi: 10.1109/ISMSIT.2019.8932819.

- [45] T. Modeer, H.-P. Nee, and S. Norrga, "Loss comparison of different sub-module implementations for modular multilevel converters in HVDC applications," in *Proc. 14th Eur. Conf. Power Electron. Appl.*, Aug. 2011, pp. 1–7.

- [46] M. Ahmadi, A. Shekhar, and P. Bauer, "Mixed redundancy strategy for modular multilevel converters in high-power applications," *IEEE Open J. Ind. Electron. Soc.*, vol. 5, pp. 535–546, 2024, doi: 10.1109/OJIES.2024.3415007.

- [47] B. Bahrani, S. Debnath, and M. Saeedifard, "Circulating current suppression of the modular multilevel converter in a double-frequency rotating reference frame," *IEEE Trans. Power Electron.*, vol. 31, no. 1, pp. 783–792, Jan. 2016, doi: 10.1109/TPEL.2015.2405062.

- [48] R. Darus, J. Pou, G. Konstantinou, S. Ceballos, and V. G. Agelidis, "Controllers for eliminating the AC components in the circulating current of modular multilevel converters," *IET Power Electron.*, vol. 9, no. 1, pp. 1–8, Jan. 2016, doi: 10.1049/iet-pel.2014.0930.

- [49] J. Han, L. M. Bieber, J. Paull, L. Wang, W. Li, and J.-N. Paquin, "Real-time simulation of hybrid three-level and modular multilevel converter based on complete equivalent model for high voltage direct current transmission system," *IEEE Open Access J. Power Energy*, vol. 9, pp. 42–54, 2022, doi: 10.1109/OAJPE.2021.3138345.

- [50] M. K. Bucher, M. M. Walter, M. Pfeiffer, and C. M. Franck, "Options for ground fault clearance in HVDC offshore networks," in *Proc. IEEE Energy Convers. Congr. Expo. (ECCE)*. NC, USA: IEEE, Sep. 2012, pp. 2880–2887, doi: 10.1109/ECCE.2012.6342371.

- [51] IEEE Recommended Practice for the Design of Reliable Industrial and Commercial Power Systems, IEEE Standard 493–2007, 2007.

SANDY ATANALIAN (Graduate Student Member, IEEE) received the B.Sc. and M.Sc. degrees in electrical engineering from the University of Balamand, Lebanon, in 2011 and 2013, respectively, and the Masters of Research (M.Sc.) degree in electrical engineering from Saint-Joseph University of Beirut (Ecole Supérieure d'Ingénieurs de Beyrouth, ESIB), in 2019. She is currently pursuing the Ph.D. degree in electrical engineering with École de Technologie Supérieure (ETS), Montreal, QC, Canada.

From 2013 to 2019, she was an Electrical Engineer with Zeenni's Trading Agency, Lebanon. From March to April 2019, she completed her Research Internship with ETS. In the summer and fall of 2023, she completed a Research Internship with Centre de Recherche d'Hydro-Québec (IREQ) under the MITACS Accelerate Program. She is a member of Group de Recherche en Électronique de Puissance et Commande Industrielle (GREPCI), ETS. Her research interests include ac/dc and dc/ac converters, multilevel converters, modular multilevel converters, control systems, and real-time simulations.

Ms. Atanalian is a member of the Order of Engineers of Quebec, the IEEE Industrial Electronics Society, the IEEE Power Electronics Society, the IEEE Transportation Electrification Society, and the IEEE Women in Engineering Society. She was a recipient of the joint-second place prize in the competition "Her Thesis in three Minutes" organized by ETS, in 2021, and the IES Student Paper Travel Assistance Award from IECON 2022, Brussels, Belgium, and from ICIT 2023, Orlando, FL, USA.

FADIA SEBAALY (Senior Member, IEEE) received the B.Sc. degree in electrical engineering from Lebanese University, in 2009, the M.Sc. degree in electrical engineering from the Faculty of Engineering-ESIB, Saint-Joseph University, Lebanon, in 2012, and the dual Ph.D. degree (Hons.) from Saint Joseph University of Beirut and the Doctoral School of Science and Technology, Lebanon, in 2016.

From 2014 to 2015, she was a Trainee with Groupe de Recherche en Électronique de Puissance et Commande Industrielle, École de Technologie Supérieure, Canada. From 2016 to 2020, she taught in the electrical engineering departments of several universities in Lebanon, including Saint Joseph University of Beirut. From 2020 to 2022, she was a Postdoctoral Researcher with École de Technologie Supérieure and a Senior Researcher with SmartD Technologies, Canada. Since June 2022, she has been a Researcher with the Grid Simulation Department, Centre de Recherche d'Hydro-Québec (IREQ). She holds a patent and reviews for several IEEE journals, including IEEE Transactions on Industrial Electronics. Her research interests include power electronics multilevel converter topologies, real-time simulations, control techniques (predictive- and sliding-mode controllers), modulation methods, motor drives, and renewable energy generation systems.

**RAWAD ZGHEIB** (Member, IEEE) received the dual master's degree from Paris, France, and Beirut, Lebanon, and the Ph.D. degree in electrical engineering from Montreal, Canada.

He is currently a Research Project Manager with G&W Electric Company involved in developing and managing proposals for government-sponsored projects and leading the execution of approved initiatives. His projects provide opportunities to develop cutting-edge

technologies and will play a pivotal role in advancing innovation strategies. He brings more than six years of expertise in research and development with a strong focus on advancing the energy transition for electrical utilities. He has successfully led innovative research projects aimed at the digitalization of electrical substations and the simulation of extreme scenarios to strengthen grid resilience-critical areas for the future of energy systems.

KAMAL AL-HADDAD (Life Fellow, IEEE) received the B.Sc.A. and M.Sc.A. degrees from the University of Québec à Trois-Rivières, QC, Canada, in 1982 and 1984, respectively, and the Ph.D. degree in electrical engineering from the Institute National Polytechnique, Toulouse, France, in 1988.

Since June 1990, he has been a Professor with the Electrical Engineering Department, École de Technologie Supérieure (ÉTS), Montreal, QC,

where he has been the holder of the Senior Canada Research Chair in electric energy conversion and power electronics, since 2002. He is a Consultant and has established very solid links with many Canadian and international industries working in the fields of power electronics, electric transportation, aeronautics, and telecommunications. He successfully transferred and implemented dozens of technologies to Canadian and international companies. His research interests include highly efficient static power converters, harmonics and reactive power control using hybrid filters, voltage level multipliers, resonant and multilevel converters including the modeling, control, and development of prototypes for various industrial applications in electric traction, renewable energy, power supplies for drives, and telecommunication.

Prof. Al-Haddad is a member of the Academy of Sciences, a fellow of the Royal Society of Canada, and a Fellow Member of the Canadian Academy of Engineering. He was the IEEE IES President, from 2016 to 2017, an IES Distinguished Lecturer, and a recipient of the 2014 IEEE IES Dr.-Ing. Eugene Mittelmann Achievement Award. He has been elected the IEEE 2022 Division VI Director elect. He is an Associate Editor of IEEE Transactions on Industrial Informatics.

. . .